## HEP 2023 Status of the ATLAS ITk Pixel Project

Sergey Kuleshov

On behalf of the ATLAS ITk Pixel Collaboration

HEP 2023

Valparaiso January 2023

## Increasing LHC luminosity: What are the challenges?

- HL-LHC luminosity ~7x10<sup>34</sup>cm<sup>-2</sup>s<sup>-1</sup>

- About x3.5 times Run-2 peak luminosity

- Increased luminosity → Increased pile-up:

- Up to 200 pile-up events expected at the LH-LHC compared to ~34 in Run-II data

- Increased pile-up compromises pattern recognition

- Increased readout rates

- Increased luminosity → Increased radiation damage

- Damage scales approximately linearly with luminosity ~x10 increase

## Phase II challenges

#### HL LHC LUMINOSITY:

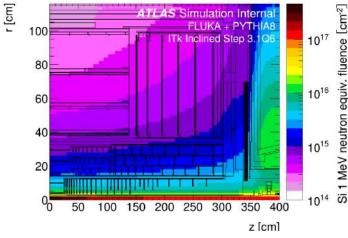

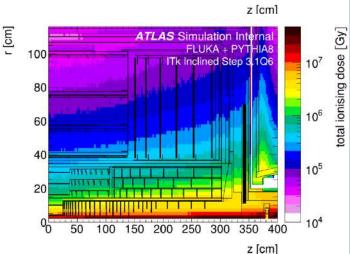

- Instant → Very high particle rates: 500MHz/cm²: pixel rates: 1-2 GHz/cm²

- Integrated→ Unprecedented hostile radiation: 10MGy(1Grad), 10<sup>16</sup> n(eq)/cm<sup>2</sup>

#### Maintain detector performance

- Smaller pixels: (25–50 x100 um²): good resolution; improved two track resolution

- Low threshold: 2500 e- → 1000e- (less signal from sensor)

- Low mass -> Low power: less average power per pixel

#### L1 challenges:

- Increased rate: 100kHz -> 1MHz

- Increased trigger latency → 3 to 20 usec

- Contribution to first/second level trigger?

| PARAMETER or<br>FEATURE    | 1st generation<br>LHC phase 0                     | 2nd generation<br>LHC Phase 1                     | 3rd generation<br>LHC Phase 2                    |

|----------------------------|---------------------------------------------------|---------------------------------------------------|--------------------------------------------------|

| CMOS technology            | 250nm                                             | 250nm / 130nm                                     | 65nm                                             |

| Max Particle Flux          | ~50 MHz/cm <sup>2</sup>                           | ~200 MHz/cm <sup>2</sup>                          | ~500 MHz/cm <sup>2</sup>                         |

| Max Pixel Flux             | 200 MHz/cm <sup>2</sup>                           | 600 MHz/cm <sup>2</sup>                           | 2 GHz/cm <sup>2</sup>                            |

| Rad. Hardness              | 1.5 MGy                                           | 3.5 MGy                                           | 10 MGy                                           |

| Pixel Dimension            | 100x150 μm <sup>2</sup><br>50x400 μm <sup>2</sup> | 100x150 μm <sup>2</sup><br>50x250 μm <sup>2</sup> | 25x150 μm <sup>2</sup><br>50x100 μm <sup>2</sup> |

| Signal Threshold           | 2500-3000 e                                       | 1500-2000 e                                       | ~1000 e                                          |

| L1 Trigger Latency         | 2-3 μs                                            | 4-6 μs                                            | 6-20 µs                                          |

| L1 Trigger Rates           | 100 KHz                                           | ~100 KHz                                          | 200-1000 kHz                                     |

| L1 Trigger<br>contribution | no                                                | no                                                | clustering info @L0<br>self-triggering           |

| ASIC side                  | ~1 cm <sup>2</sup>                                | ~4cm <sup>2</sup>                                 | 1-4cm <sup>2</sup>                               |

| Hit memory per<br>chip     | 0.1 Mb                                            | 1 Mb                                              | ~16 Mb                                           |

| Chip output<br>bandwidth   | ~40 Mb/s                                          | ~320 Mb/s                                         | ~3 Gb/s                                          |

| Power Budget               | ~0.3 W/cm <sup>2</sup>                            | ~0.3 W/cm <sup>2</sup>                            | <0.4 W/cm <sup>2</sup>                           |

**RD53**

65 nm

50 x 50 micron<sup>2</sup>

#### Hybrid pixel detector:

- fast, low power electronics

- Lot of data storage needed → local buffering

- higher VLSI integration, beyond CMOS 130nm

#### ATLAS ITK

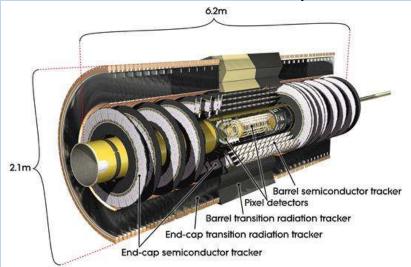

#### **Current Inner Detector System**

#### Phase-II Inner Tracker (ITk)

The current inner detector system will be replaced with a new all-silicon tracking system -- ITk

#### New tracker

- Targeting the same or better performance than current Inner Detector

- Increased granularity to maintain occupancy <1%</li>

- Low mass mechanics, cooling and serial powering to minimize material

- Increased radiation hardness

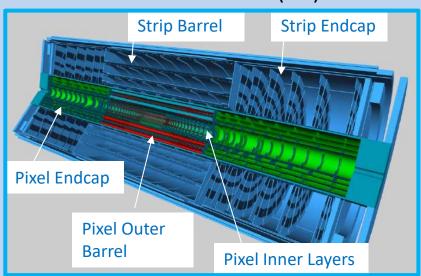

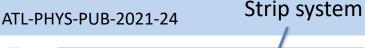

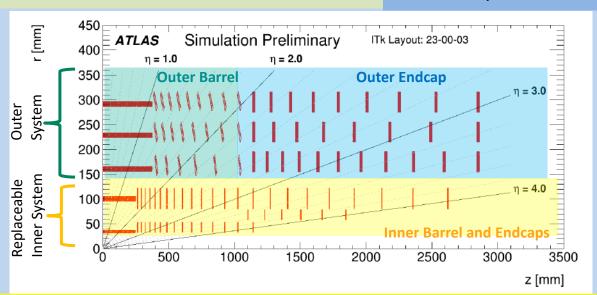

## ITk Pixel detector layout

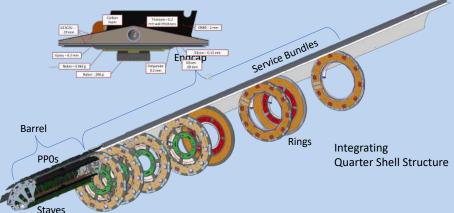

#### Outer Barrel:

3 layers of flat staves and inclined rings n-in-p planar quad modules

4772 quad modules, 6.94m<sup>2</sup>

2.3x10<sup>15</sup>n/cm<sup>-2</sup> 1.7MGy @4000fb<sup>-1</sup>

Endcap: 3 layers of rings

n-in-p planar quad modules

2344 modules, 3.64m<sup>2</sup>

$3.1x10^{15}$ n/cm<sup>-2</sup> 3.5MGy @4000fb<sup>-1</sup>

#### Current pixel system

~92M pixels

~2000 modules

~1.9m<sup>2</sup> active area

#### ITk Pixel System

~5G pixels

~9,400 modules

~13m<sup>2</sup> active area

#### Inner System Replaceable

2 layers of flat staves and rings

L0: 396 3D triplet modules and 1160 L1: n-in-p planar quad modules,

2600 modules, 2.4m<sup>2</sup>

9.2x10<sup>15</sup>ncm<sup>-2</sup> 7.3MGy @2000fb<sup>-1</sup> (Layer-0 radius=39mm 34mm)

Layout and performance described in ATL-PHYS-PUB-2021-024

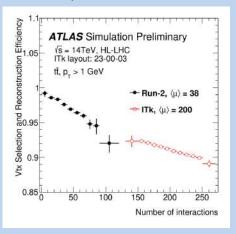

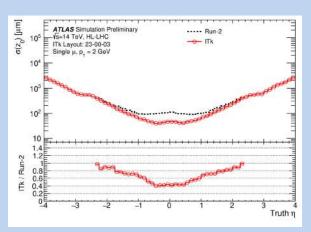

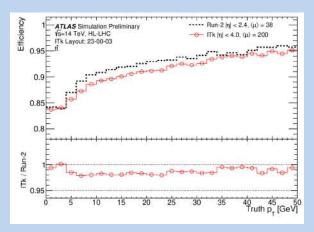

## **Performance**

# MILLENNIUM INSTITUTE FOR SUBATOMIC PHYSICS AT HIGH-ENERGY FRONTIER SAPHIR

#### Strips & Pixels

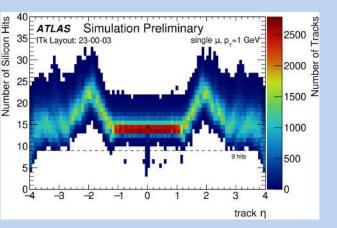

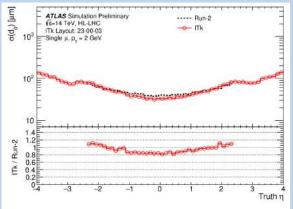

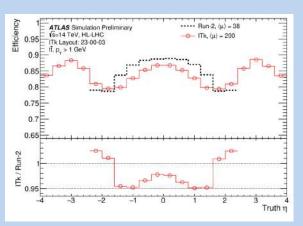

Hits vs eta, vertex reconstruction

Track d0 and z0 resolution

Track efficiency in ttbar events

Layer 0 barrel sensors  $25x100\mu m^2$ , Layer 0 ring sensors  $50x50\mu m^2$  Layers 1,2,3,4 sensors  $50x50\mu m^2$

Layout and performance described in ATL-PHYS-PUB-2021-024

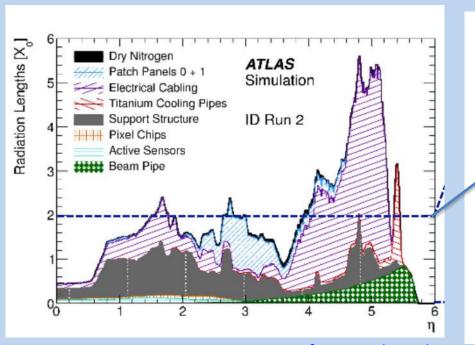

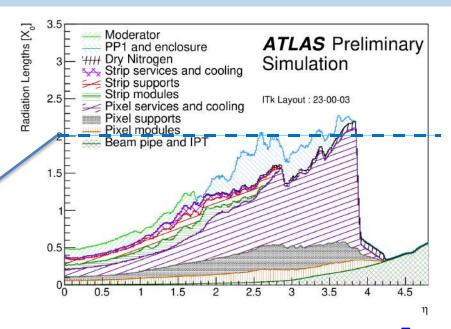

#### Material

- Reduce material using

- CO<sub>2</sub> cooling with thin titanium pipes

- Minimise material in modules using thin Si and FEchips

- Advanced powering: serial powering for pixels

- Low-mass carbon structures for mechanical stability and mounting

- Optimise number of readout cables using data link sharing

- Material distribution required for performance and radiation level studies

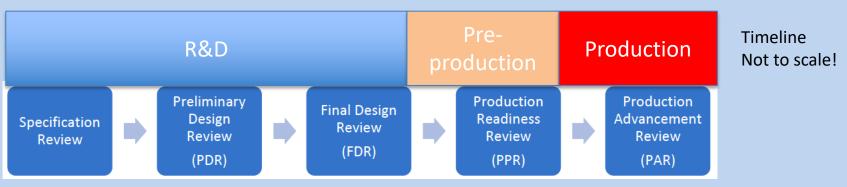

## Status of the project

#### **Project Stages**

- Specification reviews and preliminary design reviews are complete

- Completing FDR phase

- Services, Loaded Local Supports and Global Mechanics & Integration FDRs to be completed in the next months

- ASIC FDRs MOPS (pixel monitoring chip) and GBCR (data transmission) FDRs will be completed in the next few months

- Pre-production Phase

- Sensors have completed pre-production except for (25x100μm² CNM sensors)

- Pre-production of hybridization has started with initial prototyping phase to verify designs

- Pre-production of bare local supports is close to completion (early 2023)

- Production phase

- FE-ASIC ITkPixV2 production will start with an engineering run in March 2023

#### **Sensors**

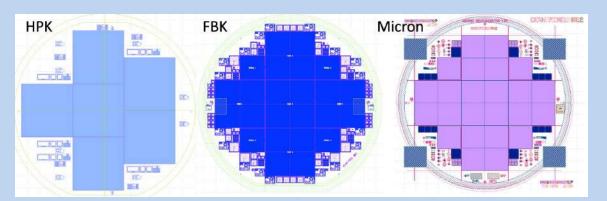

## Sensor preproduction

Planar sensor preproduction complete about 800 quad sensors from HPK (150μm),

Micron (100μm+150μm) and FBK (100μm)

See poster by Yusong Tian "ATLAS ITkPix Preproduction Planar Sensor Level Characterization for the HL-LHC Upgrade"

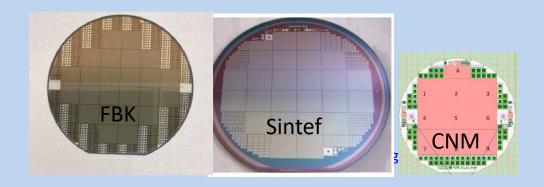

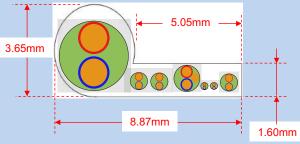

- 3D sensor preproduction close to complete

- about 160 50x50μm<sup>2</sup> sensors from FBK and Sintef sensors delivered

- About 50 25x100μm² from FBK delivered, 50 CNM 25x100 μm² due January 2023

- Measured yield found to be higher than assumed 50%

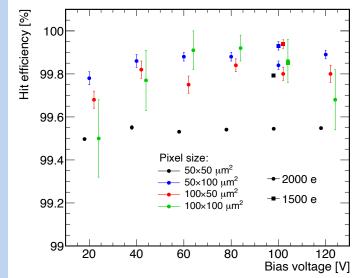

#### **Sensor Testbeam Results**

| Pixel size [µm²] | Efficiency [%] |

|------------------|----------------|

| 50x50            | 99.545 ± 0.008 |

| 50x100           | 99.84 ± 0.02   |

| 100x50           | 99.80 ± 0.03   |

| 100×100          | 98.63 ± 0.36   |

Threshold=2000e at 100V

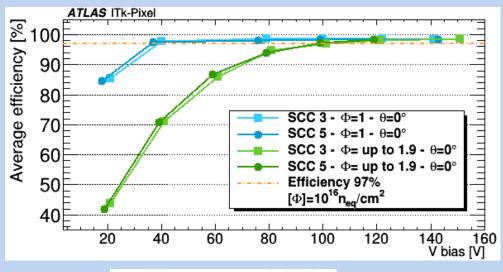

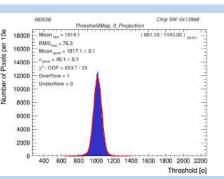

## Irradiated 3D 50x50μm<sup>2</sup> module with ITkPixV1.1 readout

- Irradiated to 1x10<sup>16</sup>n<sub>eq</sub>cm<sup>-2</sup> at Bonn

- +0.9x10<sup>16</sup>  $n_{eq}$ cm<sup>-2</sup> (peak) at PS IRRAD facility

- Threshold 1000e

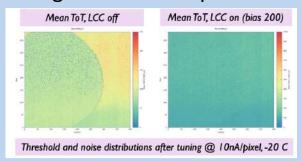

Unirradiated quad-module tested at SPS Four ITkPixV1.1 chips tuned to 2000e

• Threshold: 1983 ± 43 e

• Noise: 112 ± 12 e

Threshold and noise uniform across surface

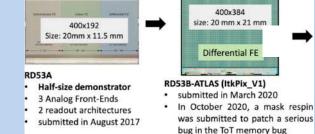

## FE-chip

- RD53 Collaboration: joint R&D for ATLAS and CMS ASIC in TSMC 65nm

- Main features for ATLAS

- 152800 pixels per chip (384 rows per 400 columns)

- 65nm technology, 50x50 μm2, total area 2x2 cm2

- Tracking in dense environments

- Low threshold operation

- Digital readout with Time over Threshold

- Radiation environment

- · Low threshold operation

- Leakage current compensation

- SEE hardening

- High data rates for 1MHz data rates

- 4 data links per chip at 1.28 Gb/s

- data compression

- Data rate studies ATL-ITK-PUB-2022-001

- Optimization of services

- · Merging of chip data in module

- Integrated shuntLDO regulator for serial powering

- Submission history

- RD53A → ITkPixV1 → ITkPixV1.1

- Final chip ITkPixV2 in final design and verification

#### Leakage current compensation

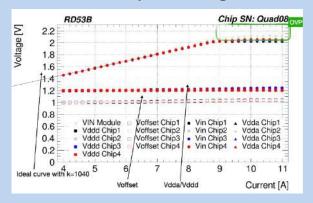

#### Serial powering

See talk by Jay Chan

"Serial powering for ATLAS ITk pixel

modules"

### Modules

- Copper content to be balanced between bump—stress (low Cu content required) and low power (high Cu content required) FEA studies indicate that around 35μm effective thickness (taking into account the area)

- High speed signals and data merging implemented

- Common hybrid for outer barrel in layers 1-4

- Triplet hybrids for LO (RO, RO.5 and linear)

#### Bump stress

- Qualify bump-strength at low temperature and after thermal cycles (-55 (-45) → +20°C) for different vendors

- cross-check with FEA and shear stress measurement

- Good results from qualification, being followed up in the pre-production

- Indium bumps need further evaluation

See poster by Jörn Grosse-Knetter "ATLAS ITk pixel module bump bond stress analysis"

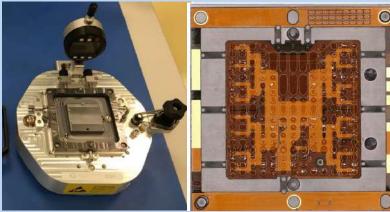

Module carrier and test setup Carrier interfaces to cooling system

## RD53A Module programme

- 31 thick modules assembled and tested for process development

- 109 thin modules assembled and tested for:

- Outer barrel cell loading

- Loading on Outer Barrel, Endcap and Inner system local supports

- Exercise production across module sites

- Site-qualification

- Extensive module QC

- Electrical readout, metrology, bump-stress, operation at low temperature and burn-in, sensor IVs

- Optimisation of glue coverage

- maximise coverage and adhesion at edge to avoid delamination

- Experience with tooling led to new tooling design

- Minimise effect of operator on glue depositon

- Relaxed the glue thickness specification

- Production revealed quality issues

- Poor dicing led to cracked chips that did not operate electrically – dicing and hybridization QC improved

- Poor bond pad quality on flexes made wire bonding diffcicult – improve hybrid QC and also bond-pad layout optimized

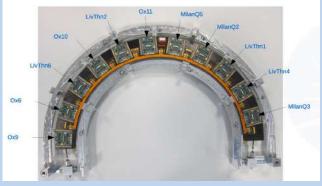

Populated endcap ½-ring with RD53A modules from different assembly and testing sites

See talk by Dimitris Varouchas "Pixel module assembly for the ATLAS ITK"

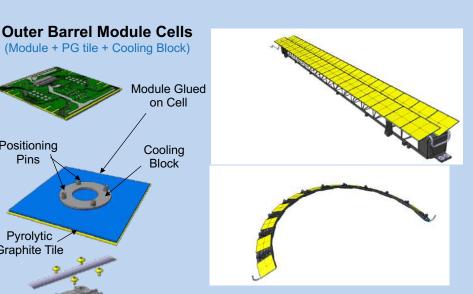

Positioning

Pins

**Pyrolytic** Graphite Tile

Cells screwed to FLS with TIM

between blocks

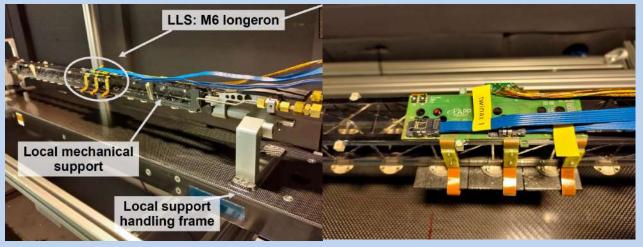

## **Local Supports**

MILLENNIUM INSTITUTE FOR SUBATOMIC PHYSICS AT HIGH-ENERGY FRONTIER

See talk by Owen Shea "Overview on current state of the art pixel mechanics for the upgrade tracking detectors at the ATLAS and CMS experiments "

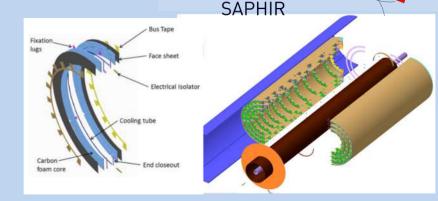

- Local supports provide stable low-mass supports for modules and services

- Critcal element is interface between module and cooling pipes

- OB modules cooled via cooling cells that interface to the cooling pipe mounted on the CF support

- Endcap and inner system use CFRP with low-mass foam and embedded cooling pipes

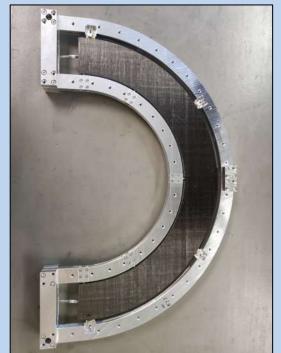

## Mechanical prototypes

Bare local support pre-production for Outer Barrel and Endcap in progress

Inner system pre-production about to start

**EC** half-ring

Prototype IS coupled ring

## **Services**

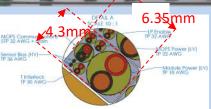

See poster by Richard Van De Wall "Highdensity high-speed service infrastructure for ATLAS ITk pixel detectors"

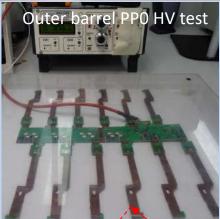

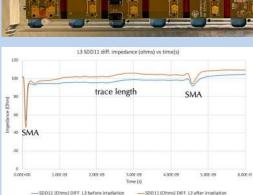

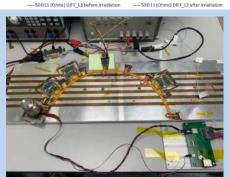

Outer Barrel Inclined L3 PPO Irradiation results on test coupons show impedance does not change

Endcap ring with ring tape & "end-of-stave card"

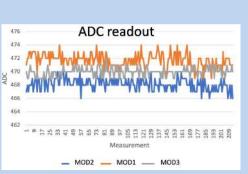

Module ADCs readout SP chain powered and modules readout

PP2 cable end

irst cable prototype: Axon cable

assembled by Glenai

power bundles (HV, LV, Canbus)

First prototypes with ribbonisation did

not work well – in discussions with

vendor

Issues with preparation of type-1

Approximate Dimensions of Woven Bundle

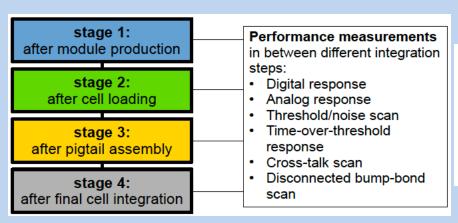

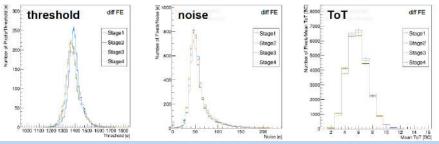

#### Loaded Local Supports and System test MILLENNIUM INSTITUTE

- Outer barrel module loading and system tests

- RD53 modules loaded on to cells and thermally tested mounted onto local supoers system test

- Performance of modules monitored through the loading process

System tests of endcap ½-ring and inner system also ongoing

## Summary

- The ATLAS Itk Pixel detector has been designed to operate in the challenging HL-LHC environment and maintain the performance of the current tracking system

- Radiation hardness

- Increased occupancy

- Low mass

- ITk pixel system has been designed to meet these challenges

- Smaller pixels

- Low mass materials

- Serial powering

- The project is completing the R&D phase and moving to production

- Large scale production brings a new set of problems

- Moving from development of individual items to a system level

- Loaded local support system tests are underway, excellent testbed for integration issues

Acknowledgement: The presentation is based on materials from Craig Buttar, ANID — Millennium Science Initiative Program-ICN2019\_044 and FONDECYT 1191103

## **BACKUP SLIDES**

## **Hybridisation**

- MILLENNIUM INSTITUTE

FOR SUBATOMIC PHYSICS

AT HIGH-ENERGY FRONTIER

SAPHIR

- Complex production process

- Hybridisation tender process complete and frame contracts placed with 4 vendors

- 4 vendors to accommodate the number of modules required

- 3 solder + 1 indium bump vendor

- Wide variety of different processing needed due to different sensors

- 3D requiring thinning and backside metalisation, 5 and 6 sensor planar wafers

- Technical issues resolved

- e.g. improved dicing but different for different vendors

- Pre-production wafers now being delivered

laser pre-grooving and dicing

blade dicing

Dicing was shown to be an issue during RD53 programme.

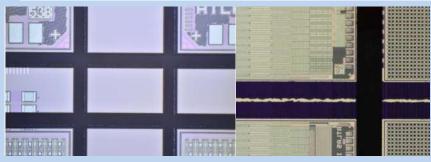

Improved dicing being used by vendors Initial studies made with dummy wafers give good results

Additional metal free region introduced around seal ring of ITkPix chip for V2 production Kuleshov 20

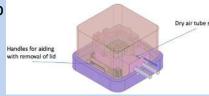

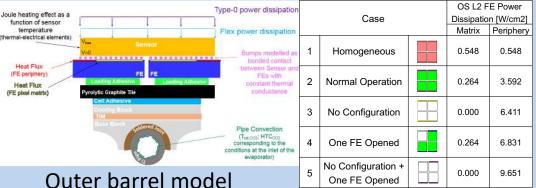

## **Thermal Management**

#### Outer Endcap

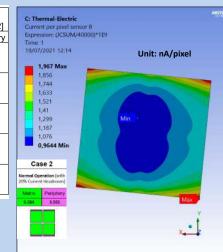

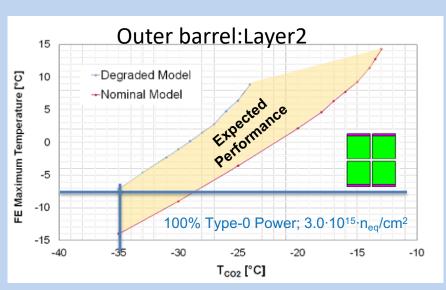

Current per pixel in the hottest sensor of L-2 Half-Ring, for the five load cases, at  $\Phi$  =  $4.59 \cdot 10^{15} \, n_{eq} \cdot cm^{-2}$

See talk by Francisca Munoz Sanchez "Carbon based local supports for the ATLAS ITk-pixel detector"

- FEA studies on all three subsystems made to evaluate thermal performance

- Sensor thermal runaway

- FE-temperature (<7°C)</li>

- Pixel leakage current (<10nA into FE-chip)</li>

- Model different power scenarios for FEchip

- Include non-uniform power dissipation

- Validated with measurements

- Local supports thermal management within specifications

Layer 2 TFM

Design: 38.8 °Kcm<sup>2</sup>/W

Degraded: 34.5 °Kcm<sup>2</sup>/W