## **Collaboration Meeting June 2019**

## Methodology to standardize the development of FPGA-based intelligent DAQ and processing systems on heterogeneous platforms using OpenCL

M. Astrain<sup>1</sup>, M. Ruiz<sup>1</sup>, S. Esquembri<sup>1</sup>, A. Carpeño<sup>1</sup>, E. Barrera<sup>1</sup>, J. Vega<sup>2</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group, Universidad Politécnica de Madrid, Madrid, Spain

<sup>2</sup>Laboratorio Nacional de Fusión, CIEMAT, Madrid, Spain

## Technical University of Madrid

With nearly 40.000 students and a annual budget of 400Me, UPM is one the leading technical universities in Spain. Its organized in 20 engineering schools and 200 Research Groups

• UPM one of the top Spanish Universities in the European Research Ranking

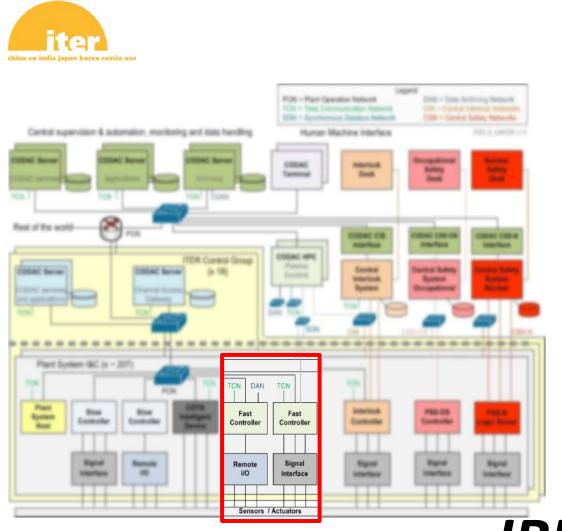

- Software development including development of EPICS device supports/drivers

- Collaborator of ITER CODAC since 2009

- Specific training in Embedded Systems, FPGA and SoCs development

- Engineers from UPM working in the EPICS community (FRIB and ITER)

### **OUTLINE**

- Motivation

- System Architecture

- OpenCL standard

- Development cycle

- Results

- Conclusions

#### Motivation

- Simplify the development and integration of advanced DAQ systems

DAQ system using FPGAs

- Can we avoid or minimize the use of Hardware Description Languages?

- Can we standardize the DAQ functionality to shift development effort only to the data processing?

- Standardize the integration of EPICS device drivers

- Can we standardize the software to simplify the development/maintenance of applications?

- asynDriver

- Nominal Device Support

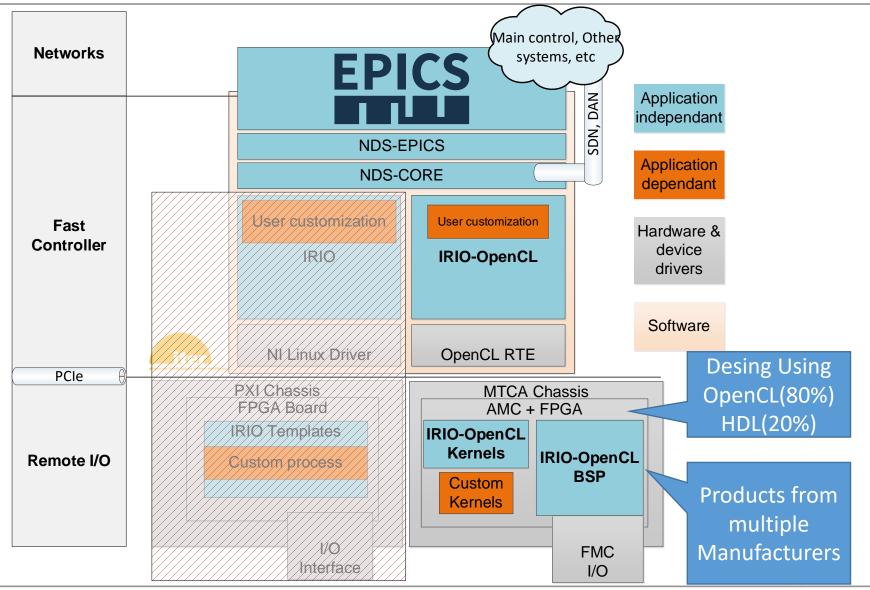

- Same API and Kernel Linux Device Driver for all hardware devices (using OpenCL).

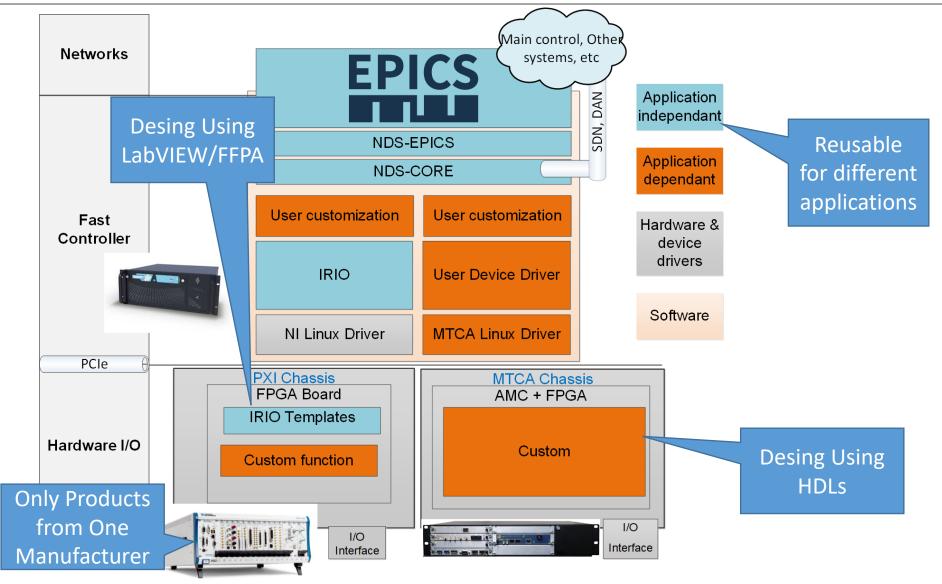

## Our previous experience with DAQ-FPGA and EPICS

IRIO https://github.com/irio-i2a2

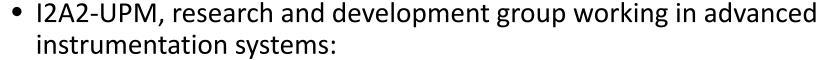

## FPGA DAQ-based systems in ITER Fast Controllers

#### Enhancements

- Simplify the development of DAQ system using FPGAs

- Can we avoid or minimize the use of Hardware Description Languages? Yes, we can use OpenCL as a high level synthesis language

- Can we standardize the DAQ functionality to shift development effort only to the data processing? Yes, we can propose a model using high level description in OpenCL with solutions already given for Data Acquisition

- Can we standardize the software to simplify the development/maintenance of applications? Yes, we can use NDSv3 modular design to separate and trace functionality changing its description in OpenCL. This functionality is even supported "in runtime" thanks to partial reconfiguration

- Let's have a look to OpenCL

## **OpenCL: Overview**

#### Implementers Desktop/Mobile/Embedded/FPGA

(intel)

EXILINX.

#### **HLS + COMPUTING MODEL**

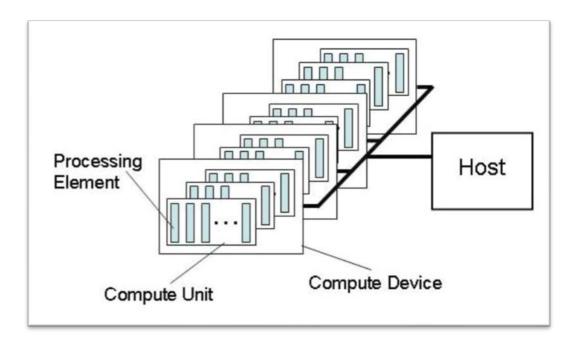

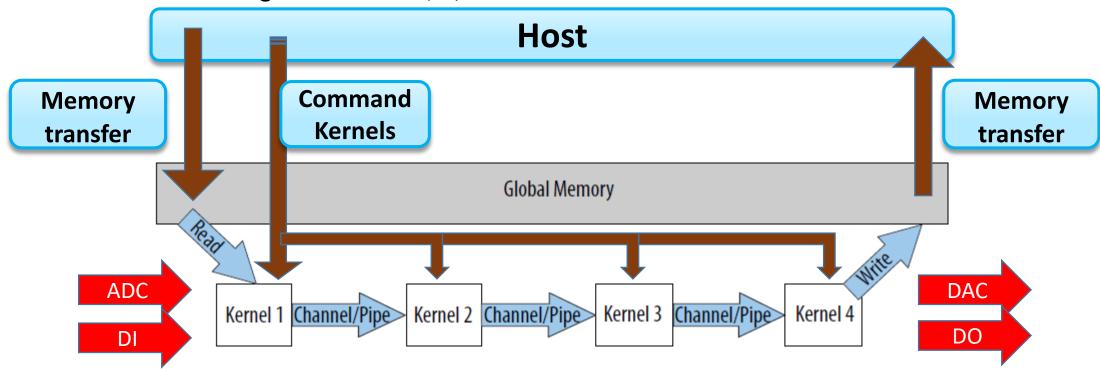

- A <u>host</u> and multiple <u>devices (CPU, GPU, FPGA)</u>

- Computation is divided into tasks called Kernels

- There is one or several **queues** that send the **Kernels** to execute concurrently

- Memory organized in <u>buffer/image</u>. Memory model

miguel.astrain@i2a2.upm.es

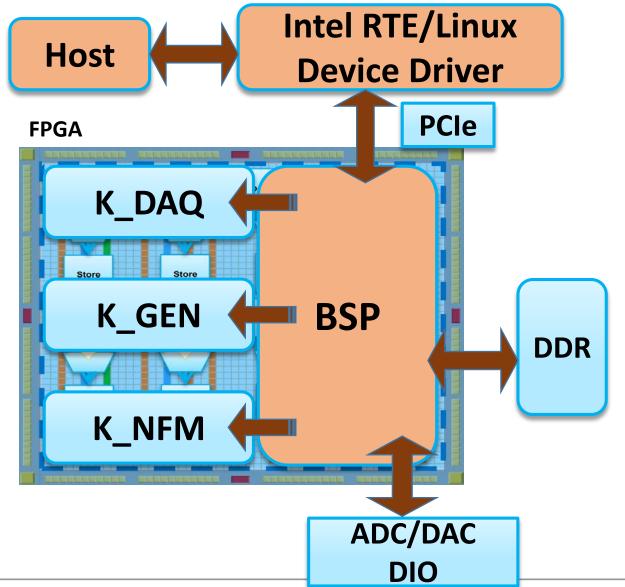

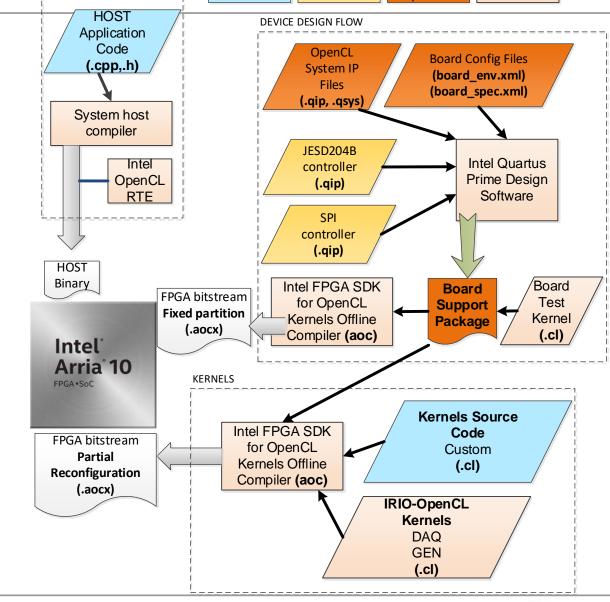

## OpenCL FPGA Device: Kernel and BSP concept

miguel.astrain@i2a2.upm.es

- Kernels: The processing pieces of OpenCL that go into the FPGA and are allocated in a specific FPGA partition to allow partial reconfiguration

- Kernels are written in C (OpenCL C).

- Kernels have access to all device memory layers

- Parallelization is achieved replicating kernels and using loop pipeline

- BSP: The part of OpenCL that goes into the FPGA and is FIXED

- Manages the access to hardware (DDR, PCIe, I/O)

- Manages the Queues to the kernels

## OpenCL Host

- Short: The part of OPENCL that goes into the C++ drivers (HOST)

- Host sends **commands** and can read/write Global Memory (**DDR**) (SLOW!) and controls kernels execution, synchronization tasks, data-flow to and from device

- Critical processes can be organized with a chain of pipes (HDL=AXI ST)

- Data can be gathered from I/O, but kernels are launched with commands

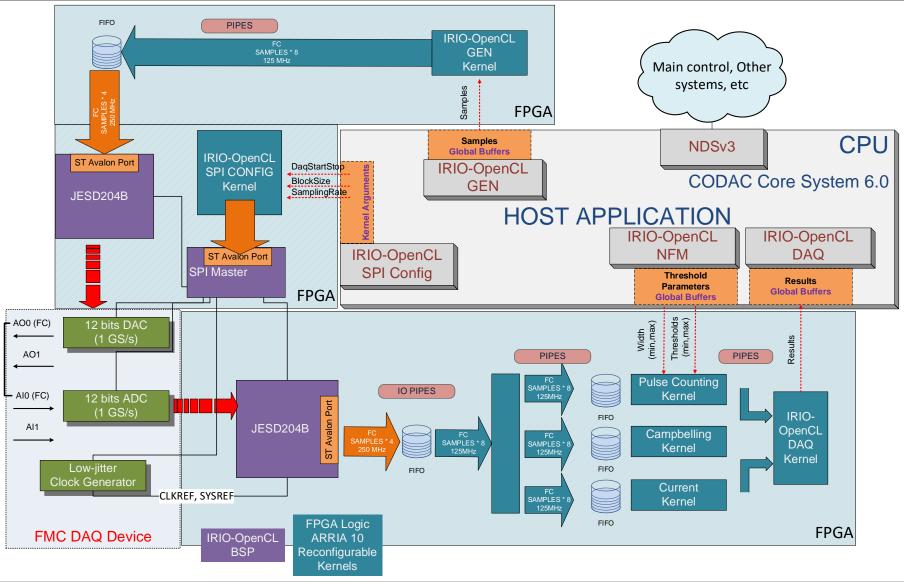

## IRIO-OpenCL

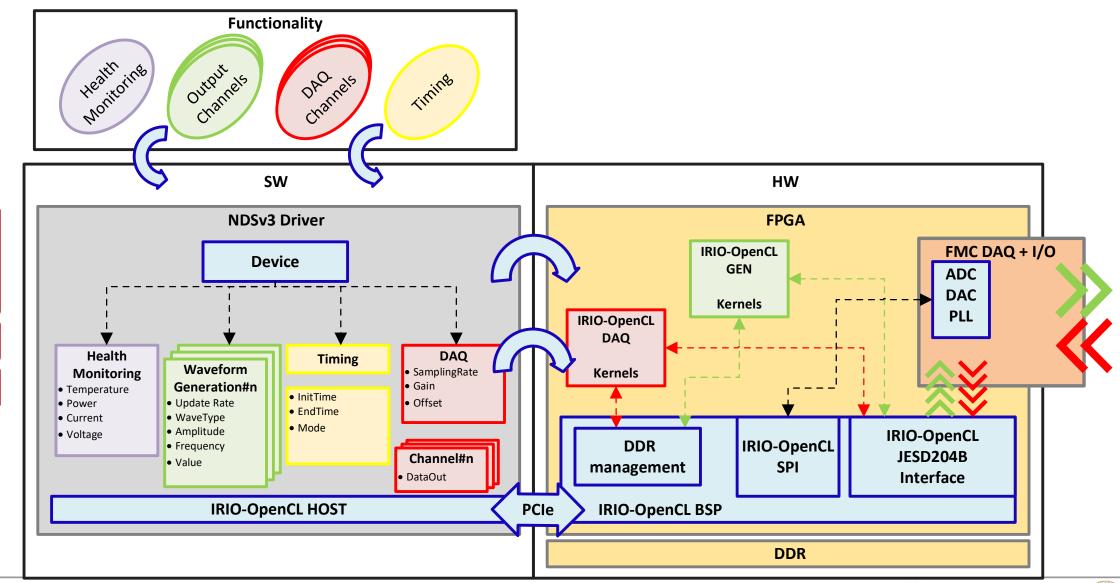

## Recap: NDSv3 + OpenCL

### Results

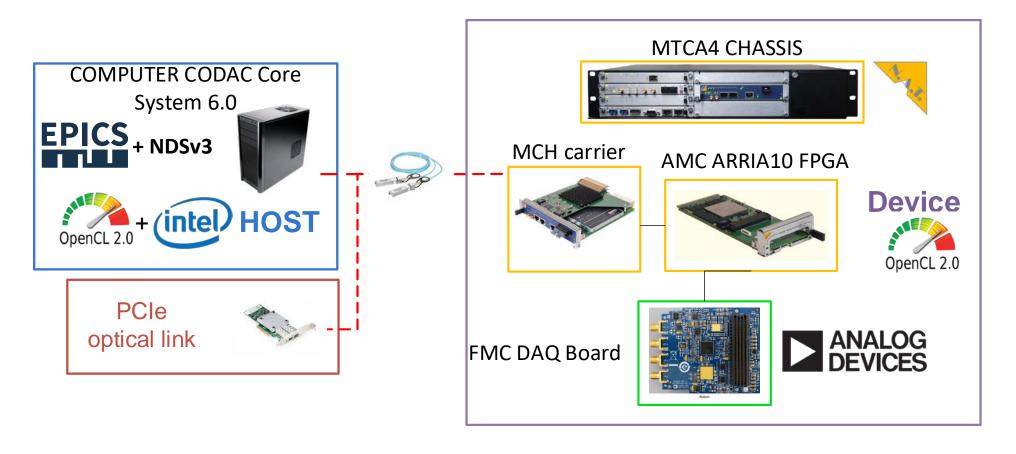

## Everything is COTS!!!

POLITÉCNICA

### Results

- Solution integrated into ITER CODAC Core System 6.0

- Simple kernel programming

- Access to profiling tools to tune performance.

- No large overhead due to the BSP (~15%)

- Implemented solution on a Neutron Flux

Measurement use case at 2 channels @ 1GS/s

- Integrated into EPICS thanks to NDSv3

- Kernel functional validation using emulation

### Conclusions

- Standardization of the development of FPGA-based DAQ devices using OpenCL

- Tested in a MTCA platform using an ARRIA 10 FPGA

- Reuse of FPGA development using an OpenCL hardware description of a DAQ device

- OpenCL enables C-like development of FPGA with lots of OpenCL algorithms examples

- OpenCL handles data transfers and device interface, hardware abstraction

- Combined with NDSv3 a modular solution was developed, simplifying the interface with EPICS. IRIO-OpenCL

- You only need to focus on "your specific algorithm"

"One driver to rule them all..."

#### Future Work

- Implementation of Machine Learning Applications

- Expand IRIO-OpenCL functionalities

- Implementation of use cases (possible collaborations) **IRIO-OpenCL Team -> Contact us!!**

**UPM** Big Science contact:

jm.cogollor@upm.es

Slide

16

POLITÉCNICA

#### **Collaboration Meeting June 2019**

Methodology to standardize the development of FPGA-based intelligent DAQ and processing systems on heterogeneous platforms using OpenCL

# Thank You! Questions?

M. Astrain<sup>1</sup>, M. Ruiz<sup>1</sup>, S. Esquembri<sup>1</sup>, A. Carpeño<sup>1</sup>, E. Barrera<sup>1</sup>, J. Vega<sup>2</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group, Universidad Politécnica de Madrid, Madrid, Spain

<sup>2</sup>Laboratorio Nacional de Fusión, CIEMAT, Madrid, Spain

## Acknowledgements

This work was supported in part by the Spanish Ministry of Economy and Competitiveness, **Projects** Nº ENE2015-64914-C3-3-R and Madrid regional government (YEI fund), Grant № PEJD-2018-**PRE/TIC-8571**

The Intel® FPGA SDK for OpenCL™ is based on a published Khronos Specification. Altera, Arria, Intel, the Intel logo, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission of the Khronos Group™. \*Other names and brands may be claimed as the property of others.

POLITÉCNICA

Development cycle hos beginned and dependant dependant of the dependant depe

Three main scenarios for a new application:

- 1- New algorithm

- **2-** New algorithm + FMC module

- **3-** New algorithm + FMC + AMC + FPGA

#### Neutron Flux Measurement