#### Analog Data Acquisition and Processing FPGA-based Solutions Integrated in Area Detector using FlexRIO technology

R. Herrero<sup>1</sup>, A. Carpeño<sup>1</sup>, S. Esquembri<sup>1</sup>, and M. Ruiz<sup>1</sup>

<sup>1</sup>Instrumentation and Applied Acoustic Research Group. Technical University of Madrid, Madrid, Spain. Email: <u>ricardo.herrero@i2a2.upm.es</u>

# Integrate FPGA IDAQs Systems in Distributed Control System EPICS with one C++ Class

#### 5-10 June 2016 Padova, Italy

### Analog Data Acquisition and Processing FPGA-based Solutions Integrated in Area Detector using FlexRIO technology

Objective

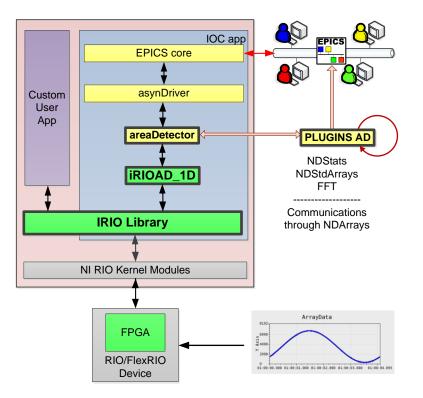

Integrate IDAQs (DAQs with FPGA) in distributed plant control systems like EPICS:

- Better performance and preprocessing capabilities, reduce time delays.

- Dificult to Integrate, heterogeneuos devices → areaDetector brings common interface to EPICS to different imaging hardware solutions

#### 5-10 June 2016 Padova, Italy

### Analog Data Acquisition and Processing FPGA-based Solutions Integrated in Area Detector using FlexRIO technology

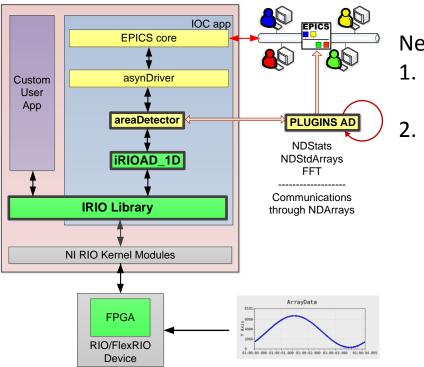

New model, two parts:

- 1. FPGA common model Design Rules to show common interface

- New areaDetector 1-D driver Connect IDAQ hardware Interface with EPICS through new PVs Reuse areaDetector model (asynNDArrayDriver) and some PVs Reuse areaDetector plugins

FPGA

**1-D** areaDetector

for IDAQs (FPGA)

### Analog Data Acquisition and Processing FPGA-based Solutions Integrated in Area Detector using FlexRIO technology

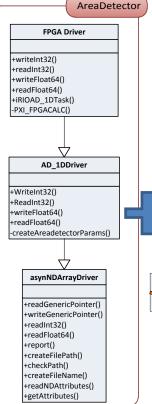

New *HW developments* just need to follow *FPGA Design Rules* & Develop just one class for the specific parameters of the EPGA th

Develop just one class for the specific parameters of the FPGA that connects to AD\_1D driver