# FPGA Implementation of Toeplitz Hashing Extractor for Real Time Post-processing of Raw Random Numbers

Xiaoguang Zhang, You-Qi Nie, Hao Liang, Jun Zhang Department of Modern Physics, University of Science and Technology of China State Key Laboratory of Technologies of Particle Detection & Electronics, Hefei, China

The way to transplant Teoplitz hashing extractor from computer to a resource limited FPGA.

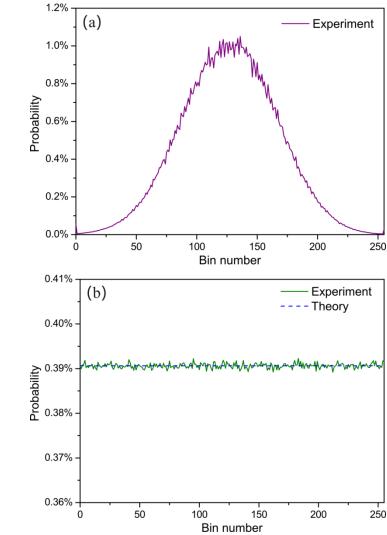

Probability distribution of  $10^7$  raw samples (a) and  $10^7$  extracted random bits (b).

## **Experimental Results**

The real time post-processing speed reaches above 3.36 Gbps

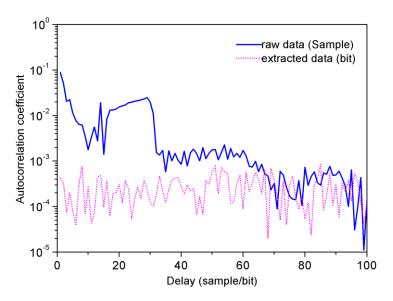

Autocorrelation analysis for  $10^7$  raw samples and  $10^7$  extracted random bits.

### Poster

According to the above ideas, in terms of specific implementation, we choose k=80 and design three computing units in FPGA working in a pipeline mode as is shown in Fig. 2. These units are working with a synchronized clock of 62.5 MHz. With such configuration,

Fig. 2 FPGA implementation of Toeplitz hashing randomness extractor

rate of unbiased true random bits reaches 3.36 Gbp.

Hardware design

Results

#### Ideas to realize the Toeplitz Hashing extractor in FPGA

#### References

Fig. 5 (a) Probability distribution of 10<sup>7</sup> raw Samples and (b) 10<sup>7</sup> extracted random bits.