# Online calibration of the TRB3 FPGA TDC with DABC software

Jörn Adamczewski-Musch, Sergei Linev, Cahit Ugur, GSI, Darmstadt, Germany

## TRB3 hardware

- 5 Lattice ECP3-150EA FPGAs

- 4 peripheral FPGAs as TDCs

- 1 central FPGA for trigger system and GbE

- TrbNet (control) and UDP/IP/GbE (data)

- various add-on boards (ADC, PADIWA,..)

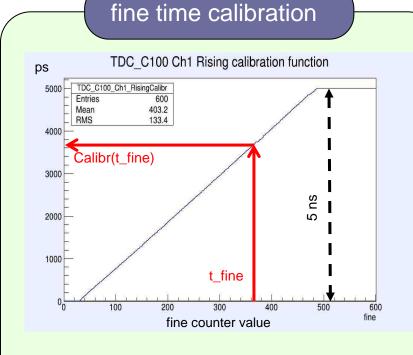

t\_stamp = ( epoch \* 2048 + t\_coarse ) \* 5ns - Calibr(t\_fine)

- required per each TDC channel (~ 48) for each FPGA design

- may frequently measure calibration tables from uniform-distributed fine times

- may use known temperature dependency function

- can be done during data taking with DABC event builder software

- precision ~ 10 ps (without calibration: 200 ps)

# Poster Session 1 Poster 76

The TRB3 collaboration

FAIR Facility for Antiproton and Ion Research

### Online calibration of the TRB3 FPGA TDC with DABC software

Jörn Adamczewski-Musch, Sergei Linev, Cahit Ugur, GSI, Darmstadt, Germany

The TRB3 - Trigger Readout Board - features 4 FPGA based TDCs with a total of up to 264 channels and a time precision of 8 ps RMS [1]. It was applied for various beam tests and is going to serve as a standard DAQ hardware for FAIR detectors, such as HADES, PANDA, and CBM. To achieve the best time precision, however, each TDC channel must be calibrated individually.

First of all, fine counter calibration should be done by means

of random test inputs and it should be repeated, if the or random test inputs and it should be repeated, if the calibration function changes (in most cases due to temperature change). Alternatively, temperature dependency of each channel can be calculated in advance and compensated using the temperature information from the sensors around the FRGAs. Another compensation should be applied to the mean value deterioration caused by the temperature change. And finally, stretcher latency (used for ToT measurements), which also depends on the temperature change, should be measured in advanced and

compensated during the measurement.

All these calibration tasks can be carried out already during data taking within the event building DAQ software DABC.

Produced time values can either be stored with the original raw data or replace them. The calibration analysis code has been implemented with the C++ stream framework and can run as plug-in for DABC as well as with ROOT-based analysis ents, like HYDRA or Go4

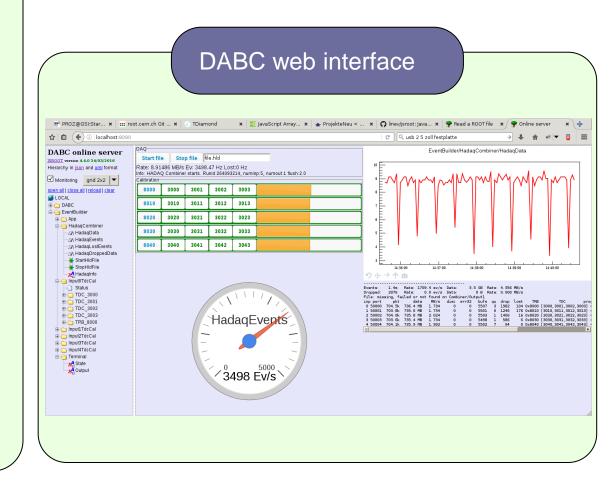

An HTTP server in the DABC process provides online monitoring and control of the TDC calibration from a standard web browser.

[1] C. Ugur, S. Linev, J. Michel, T. Schweitzer, M. Traxler, ovel approach for pulse width measurements with a high cision (8 ps RMS) TDC in an FPGA,2016 JINST 11 C01046

#### Online software

Data acquisition for TRB has been implemented with DABC framework (http://dabc.gsi.de). UDP packets, retrieved from several TRB boards, are verified, sorted and combined together into HLD formatted events, which are then stored on disk.

formatted events, which are then stored on disk. The code for PEAR TO calibration and temperature compensation has been implemented with C++ based steem framework (IMEAR INFLIGHT AND TO AND

#### TRB3 hardware

- Main board with 5 Lattice ECP3-150EA FPGAs

- 4 peripheral FPGAs as TDCs with up to 260 channels central FPGA for trigger system and GbE controller TrbNet (control) and UDP/IP/GbE (data) protocols

- 4 highspeed 208 pin connectors for various AddOns:

- 6 port hubs, NIM/ECL input, ADC, 100mil pins, PADIWA. reduced variant TRBsc exists (1 FPGA each for 19" crate system)

#### Timestamp counters

Dump of acquired TRB3 TDC data with DABC hldprint utility:

The hit time t\_stamp is evaluated from epoch marker, coarse counter t\_coarse and calibrated fine counter t fine, as denoted by different colors:

t stamp = ( epoch \* 2048 + t coarse ) \* 5ns - Calibrit fine)

The Time over Threshold T\_o\_T is derived from consecutive hits with "rising edge" and "falling edge" properties ("isrising" 1 or 0):

$T_o_T = t_stamp_{tallow} - t_stamp_{tallow}$

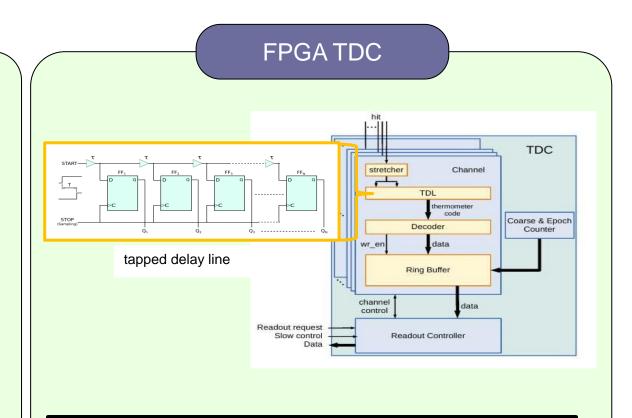

#### **FPGATDC**

TRB3 FPGATDC uses tapped delay line (TDL) technique: Fine time stamp of an incoming signal is derived from the number of delay elements which the signal propagates from arrival until the next 200 MHz readout clock edge stops such sampling. For time over threshold (ToT) measurements, trailing edge is shifted by a stretcher to subsequent readout clock cycles

#### Statistical calibration approach

Assuming input signals with an uniformly fine time distribution, the TDC fine time counter values should also be uniformly distributed in the ideal case. The measured deviations from such uniform distribution can be used to evaluate a fine time counter calination Calibri, Pie-Piectally this can be implemented as lockup-table or as parametrized function. This calibration requires, however, a sufficient statistics of acquired time values (thist) or each TDC channel. The calibration procedure may be performed with special triggered signals either once before the actual detector data taking, or it may be repeated frequently, e.g. during accelerator spill pauses

#### DABC web interface

The complete DAQ process, including data taking, TDC calibration and files storage, can be monitored and controlled by a web interface. One can also access various histograms produced in the TDC calibration process. This web UI has been implemented using the JavaScript ROOT library (https://root.cem.ch/js/).

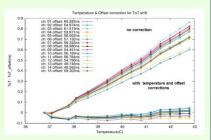

#### Temperature dependency

Temperature significantly affects the FPGA TDC fine-counter calibration function. A difference of several degrees K leads to increase of timing errors in 20-40 ps, which is much higher than obtained 8+12 ps resolution of a TDC with constant temperature. To avoid such effects, temperature should be stabilized or calibration should be repeated constantly, taking into account any possible changes.

TDC C100 Ch1 Rising calibration function

Figure shows the calibration function for the same channel, measured with temperatures 28, 35 and 44 °C. These calibrations look very similar except for a scaling factor. This can be described by a linear function

Calibr<sub>(fine)</sub> = Calibr<sub>(o</sub>(fine)  $\times$  (1 + 0.0044  $\times$  (t - t0))

The described correction compensates most temperature effects on fine-counter calibration. Since a temperature sensor near each FPGA TDC is continuously read out, such correction can be applied online during data taking. The resulting precision of time measurement in ±5 °C temperature range remains below 18 ps.

#### ToT temperature corrections

Time over Threshold (TOT) values measured with the FPGA TDC are also affected by temperature. Both the fine time counter calibration and the stretcher offset for the trailing edge signal are temperature dependent. This deterioration of -100 ps/ °C can be compensated by individual channel calibration with a pulser signal of known TOT. Such correction can be applied in stream/DABC software already during data taking, since the actual temperature data is also read out from the FPGA. Taken from [1]