## "NaNet: FPGA-based Network Interface Cards Implementing Real-time Data Transport for HEP Experiments"

## Michele Martinelli PhD Student

on behalf of NaNet collaborations

R. Ammendola<sup>1</sup>, A. Biagioni<sup>2</sup>, O. Frezza<sup>2</sup>, G. Lamanna<sup>3</sup>, F. Lo Cicero<sup>2</sup>, A. Lonardo<sup>2</sup>, M. Martinelli<sup>2</sup>, P. S. Paolucci<sup>2</sup>, E. Pastorelli<sup>2</sup>, L. Pontisso<sup>4</sup>, D. Rossetti<sup>5</sup>, F. Simula<sup>2</sup>, M. Sozzi<sup>4</sup>, P. Cretaro<sup>2</sup>, P. Vicini<sup>2</sup>

¹Sezione di Tor Vergata, Istituto Nazionale di Fisica Nucleare, Rome, Italy, ²Sezione di Roma, Istituto Nazionale di Fisica Nucleare, Rome, Italy, ³Laboratori Nazionali di Frascati, Istituto Nazionale di Fisica Nucleare, Pisa, Italy, ⁵nVIDIA Corp, Santa Clara, CA, USA

## NaNet

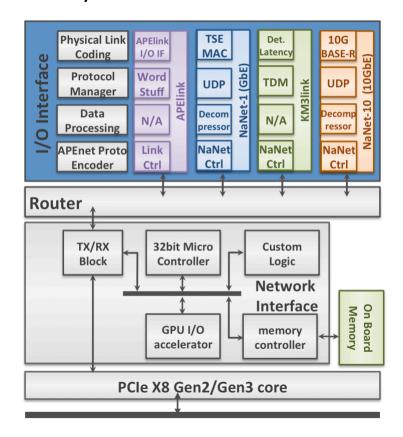

NaNet project goal is the design and the implementation of a family of FPGA-based PCIe Network Interface Cards implementing low-latency, real-time data transport between its network channels and the the CPU/GPU memories.

A reconfigurable processing module is also available to implement applicationspecific processing on inbound/outbound data streams with highly reproducible latency.

NaNet-1 is based on Altera Stratix IV dev board

As of now NaNet design has been specialized in:

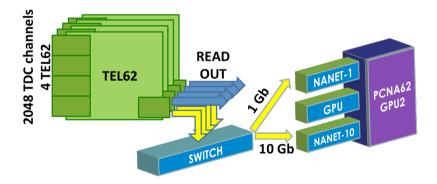

- 1. NaNet-1 (single 1GbE port)

- 2. NaNet-10 (four 10GbE ports)

employed in the GPU-based real-time trigger of the CERN NA62 experiment

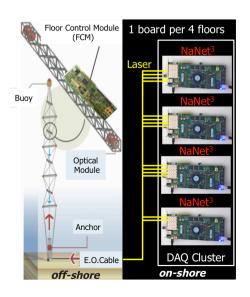

3. NaNet3 (four 2.5 Gbit optical channels)

adopted in the data acquisition system of the KM3NeT-Italia underwater neutrino telescope.