para Imagen Molecular

# Instituto de Instrumentación

# PLAS: A 32-CHANNEL, DEAD TIME-LESS ANALOG MEMORY ASIC FOR THE TRACE DETECTOR

**R. J. Aliaga**<sup>1\*</sup>, V. Herrero<sup>2</sup>, S. Capra<sup>3</sup>, J. A. Dueñas<sup>4</sup>, A. Pullia<sup>3</sup>, A. Gadea<sup>1</sup>, D. Mengoni<sup>5</sup> \*Contact: raalva@ific.uv.es

#### **PURPOSE**

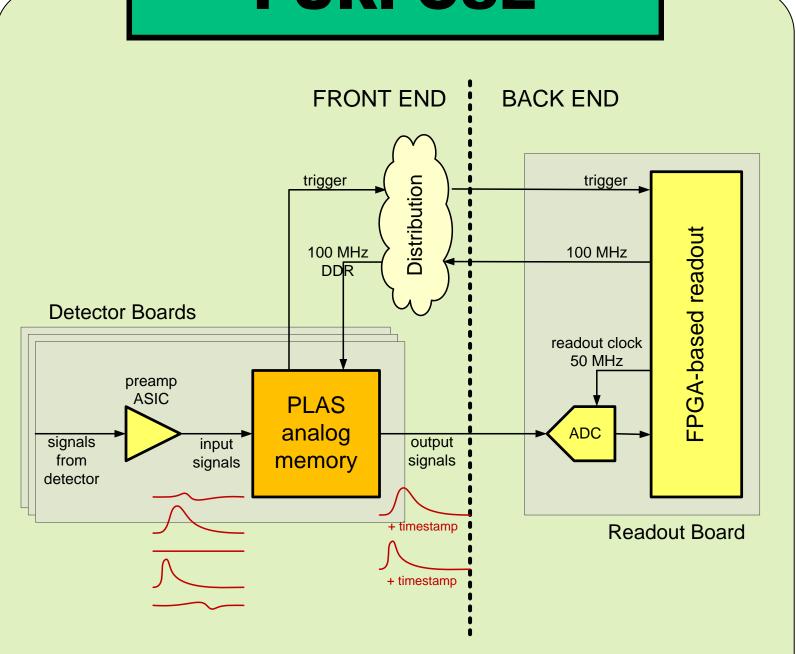

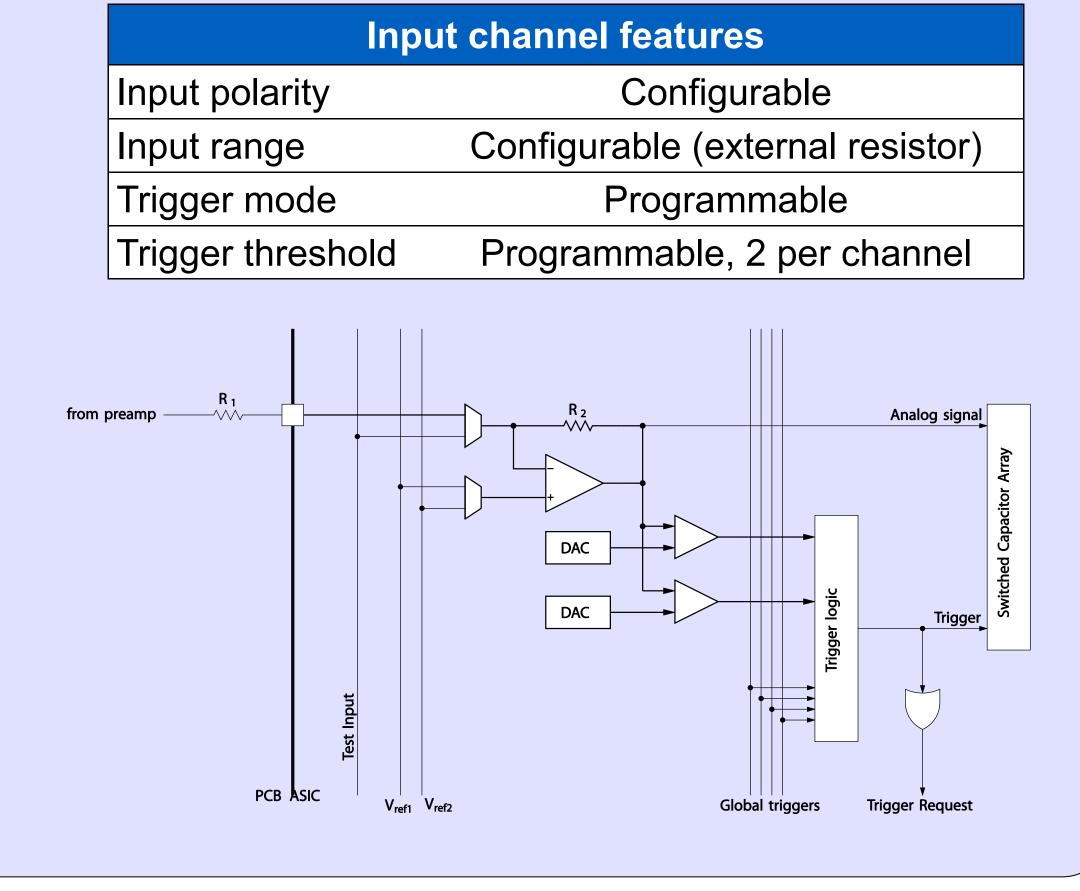

PLAS is a low power, compact ASIC for the TRACE front-end that carries out:

- zero suppression

- local triggering

- timestamping

- pulse sampling

- serialization

## **ANALOG MEMORY ARCHITECTURE**

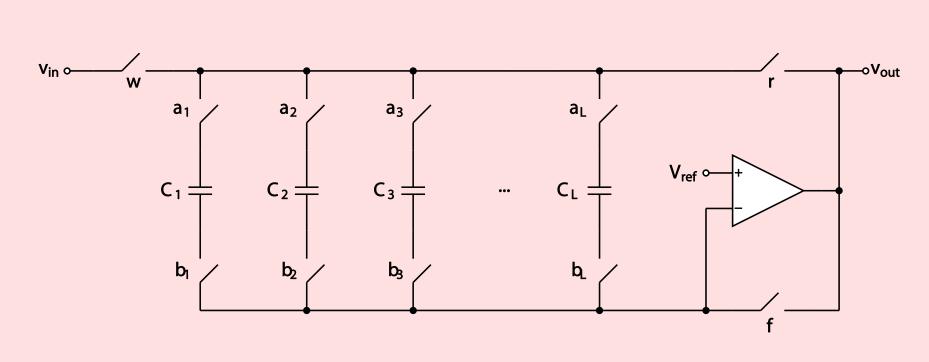

## SCA (Switched Capacitor Array)

Typical analog memory circuit: one SCA per channel.

- Capacitors sequentially connected to bus to write analog voltage values until stopped by trigger.

- Read out later one by one and digitized externally.

- High write frequency, low read frequency.

Problem: Cannot be rewritten until read out. Limited by read frequency. Very long dead time.

Existing solutions: Partial readout, channel replication.

# SCA channel 192 cells SCA channel 192 cells SCA channel 32 cells

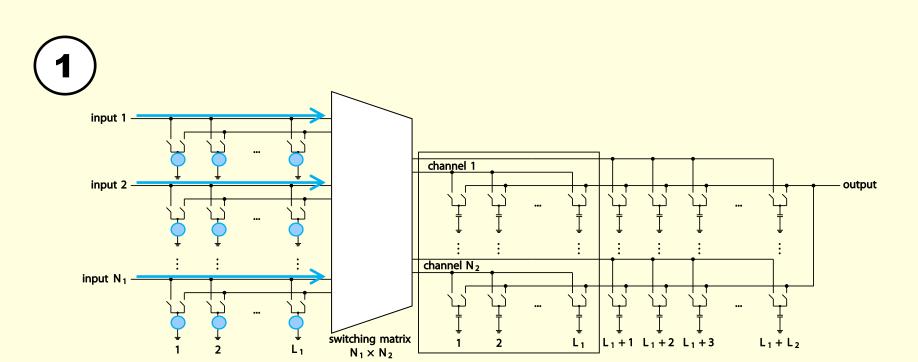

PLAS (PipeLined Asymmetric SCA)

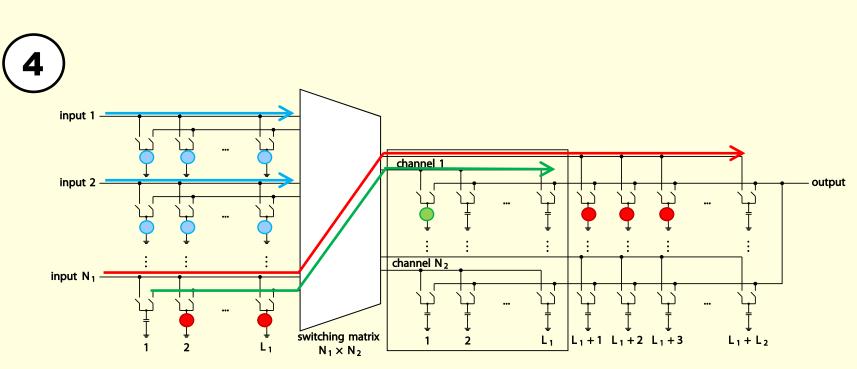

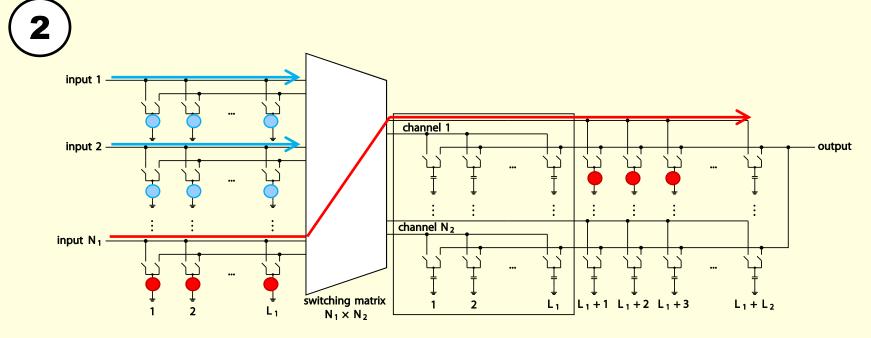

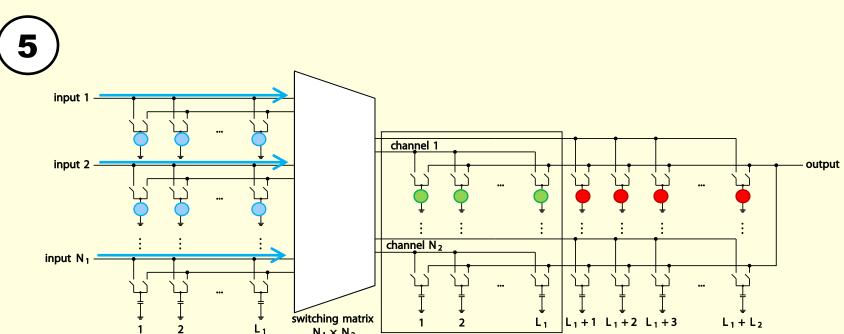

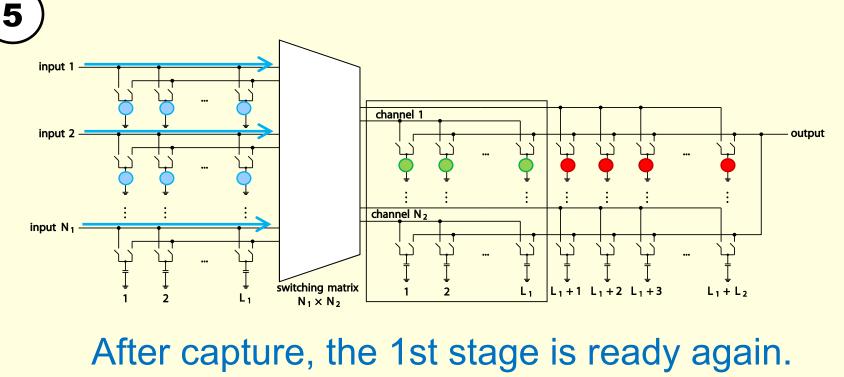

**New solution:** Split the memory into two sequential SCA stages.

- Stage 1: One short SCA per channel for pre-trigger samples.

- Stage 2: A few slots containing one long SCA for post-trigger samples and one short SCA to store a copy of Stage 1.

Advantages: no deadtime, reduced number of cells **Disadvantages:** more complex calibration, noisier pre-trigger

Simultaneous capture of different

channels is possible.

The captured pulse samples are

read out later at a slower rate.

#### PRINCIPLE OF OPERATION

The 1st stage is sampling like a circular buffer.

During capture, 1st stage samples are copied to a buffer in the 2nd stage.

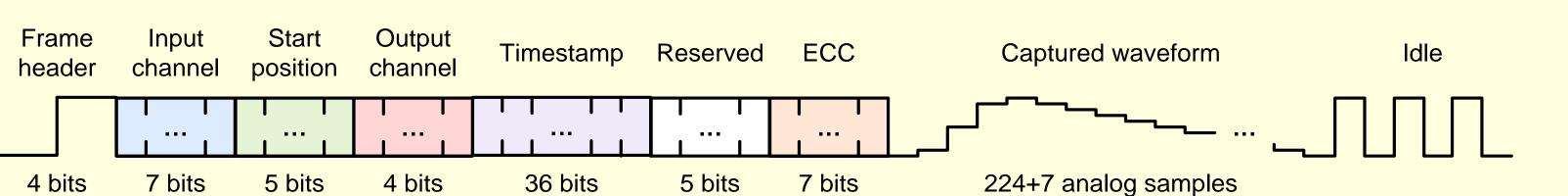

Readout is organized in frames with analog samples and digital data (timestamp and internal tracking).

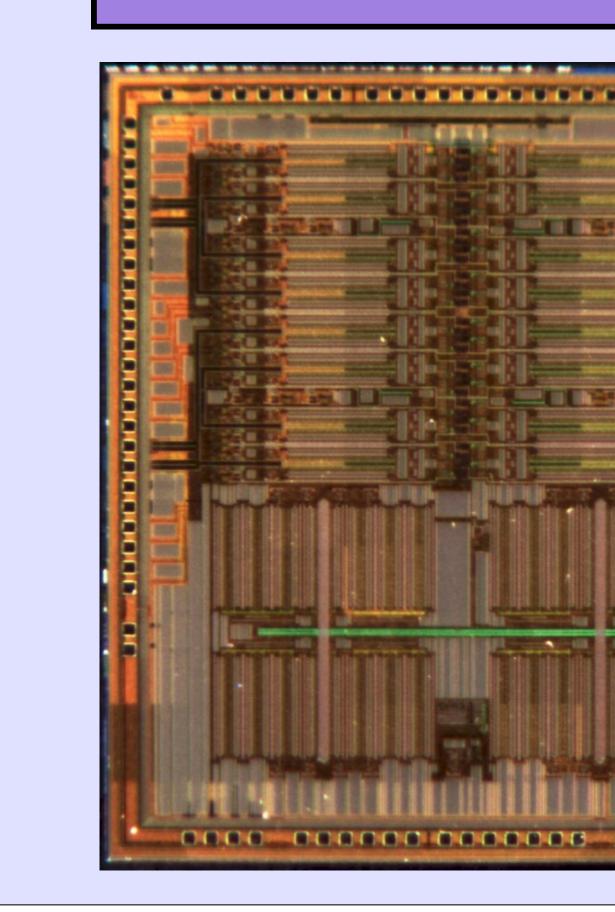

0.18µm CMOS

$3.5 \times 3.9 \text{ mm}^2$

32

224 per slot

(32 pre-trigger + 192 post-trigger)

200 MHz (100 MHz DDR)

50 MHz

1.8 V

0.3 V to 1.5 V

100 MHz

11.9 **ENOB**

10 mW/channel

PLAS prototype specifications

Technology

Input channels

Queue slots

Memory depth

Write frequency

Read frequency

Power supply

Internal range

Input bandwidth

Power consumption

Output noise

Die size

Capture continues at a free On trigger, the channel is locked. slot in the 2nd stage.

No deadtime.

$(\mathbf{6})$

#### **PROTOTYPE**

Poster presented at the 20<sup>th</sup> Real Time Conference - June 2016, Padova, Italy.

Partially supported by the Spanish Ministry of Economy and Competitiveness (MINECO) under Grant FPA2014-57196-C5, the Generalitat Valenciana, Spain, under Grant PROMETEOII/2014/019, and the European Comission FEDER funds.

Simulated performance