## 20<sup>th</sup> IEEE Real Time Conference Jun.8<sup>th</sup>, 2016 Padova (Italy)

## uSOP: a microprocessor-based Service-Oriented Platform for Control and Monitoring

A. Aloisio, F. Di Capua, R. Giordano, P. Scotto di Vetta

Dipartimento di Fisica, Univ. di Napoli Federico II and INFN

A. Anastasio, V. Izzo, G. Tortone

INFN - Sezione di Napoli

F. Ameli

INFN - Sezione di Roma

P. Branchini

INFN - Sezione di Roma Tre

#### Overview

- uSOP: a <u>Service-Oriented Platform for embedded</u> applications

- Hardware

- Software

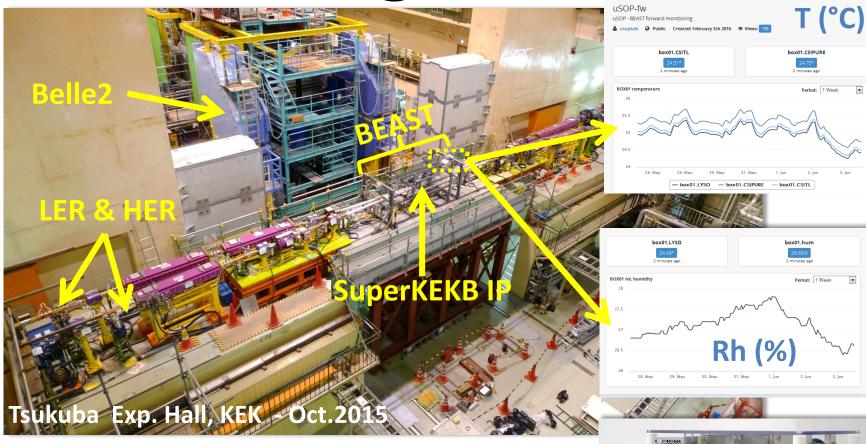

- uSOP at work: monitoring @ KEK Laboratory

- Belle2, Beast

- Future plans

- Conclusions ...

- ... and one for aficionados of manga 漫画 ...

Belle2 detector, KEK (J)

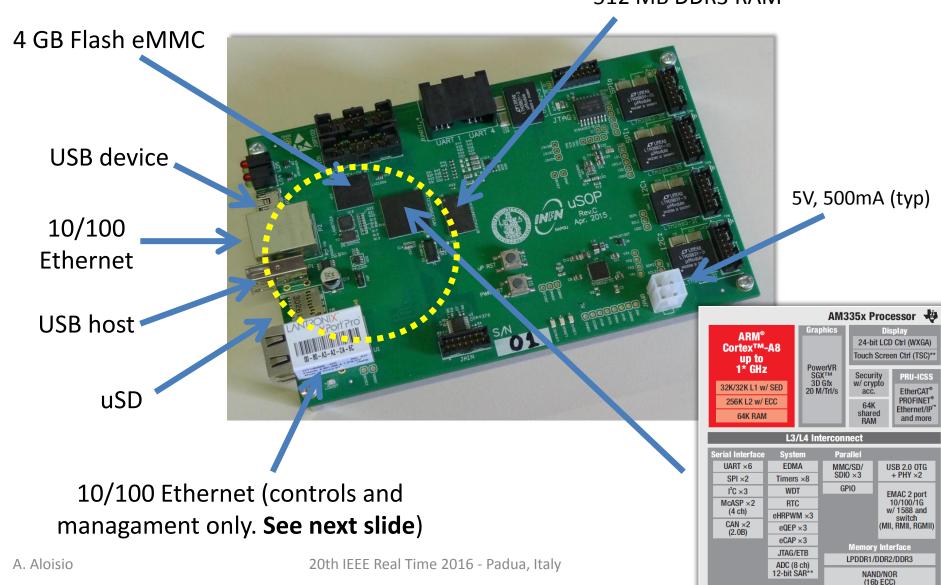

The uSOP board

#### uSOP

- <u>u</u>P- based, <u>Service-Oriented</u>

<u>P</u>latform for embedded applications

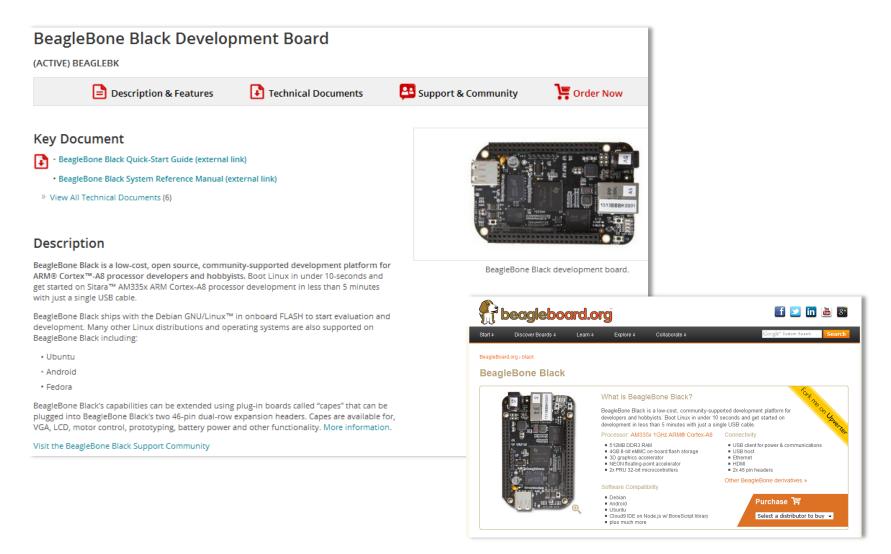

- Designed for slow-controls the Belle2 experiment (KEK-Tsukuba, J)

- Strongly oriented to SPI, I2C, JTAG, UART, with isolated power for peripherals and sensors

- Fully managed remotely

- Running Linux OS (Debian)

- 3U Eurocard native form factor, expandable

- Derived-from and compatible-with BeagleBone Black open-source project

#### **LET'S SPEAK**

#### uSOP – uP and utilities

512 MB DDR3 RAM

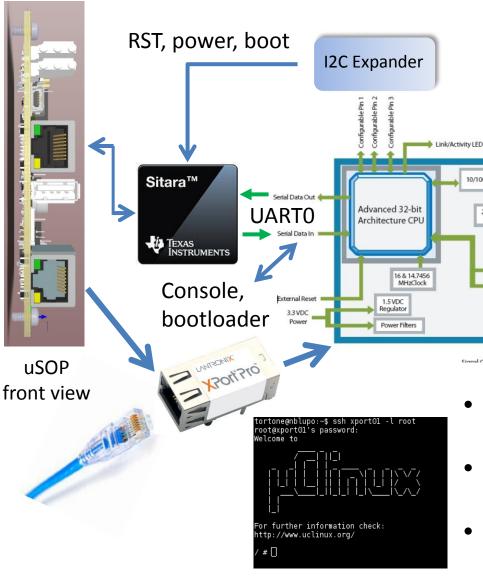

#### Remote Management

10/100 PHY

25 MHz

- Remote control over IP for:

- uP RST

- Boot mode

- Power on/off

#### **UART** over IP:

- Console

- Bootloader

- More tasks can be implemented (watchdog, controls, ...)

- Based on the latest version of Lantronix Xport-Pro

10/100

Ethernet

mit & Receive

Shield Tabs

Isolation

& Filtering

16 Mbytes Flash Memory Ethernet

- μP Freescale MCF5208, MMU-less architecture, 8MB RAM, 16MB Flash

- SoC running uCLinux with a full cross-compiled SDK

**Timers PWM** uSOP - Peripherals/Intf **Event Capture PRU** Pace Scientific 16 x GPIO **TCK** JTAG (\*) TDI 2 x RS232 (\*) FPGA firmware download 2 x SPI (\*) 2 x I2C (\*) = fully isolated, 5V-12V supply = buffered 4 x 12 bit AIN (\*\*) + 2 on-board power monitoring

#### **SOFTWARE**

## Linux porting

- Linux distribution: Debian armv7l

- image-builder script to generate a Linux Debian rootfs image for operating system installation on eMMC or network booting

- Full support for compilers and applications (packages management via APT repository)

- Kernels: major releases available

- 3.x (up to 3.8.13 with Xenomai Real-Time Linux support)

- 4.x (up to 4.5.0)

- bootloader: U-Boot

- some patching done on official TI bootloader in order to enable network booting and boot media selection (eMMC, uSD, network)

- first stage boot available:

- eMMC

- uSD

- UART (XModem/YModem protocol)

- Ethernet (DHCP + TFTP)

- Linux boot available

- eMMC

- uSD

- Ethernet (TFTP)

- Devices for root filesystem (rootfs) mounting:

- eMMC

- uSD

- Ethernet (NFS)

## **Experimental Physics and Industrial Control System**

- EPICS (<a href="http://www.aps.anl.gov/epics/">http://www.aps.anl.gov/epics/</a>) is a set of Open Source software tools, libraries and applications developed collaboratively and used worldwide to create distributed soft real-time control systems for scientific instruments such as a particle accelerators, telescopes and other large scientific experiments.

- On uSOP:

- Straightforward compilation on ARM

- Variety of EPICS extensions available on board:

- ALH (ALarm Handler)

- PV gateway

- Asyn

- StreamDevice

- Autosave

- IOCs for:

- Linear LTC2499 (I2C)

- Linear LTC2983 (SPI)

- Sitara ADC (parallel)

#### On XportPRO

- uCLinux customization, to enable additional software packages and security reinforcement of network services (SSH vs telnet)

- Custom, low-footprint EPICS implementation, cross-compiled for uCLinux

- IOCs for:

- I2C protocol software emulation

- SITARA power control

- SITARA first stage boot setting (eMMC, Ethernet, uSD, UART)

- LED activity

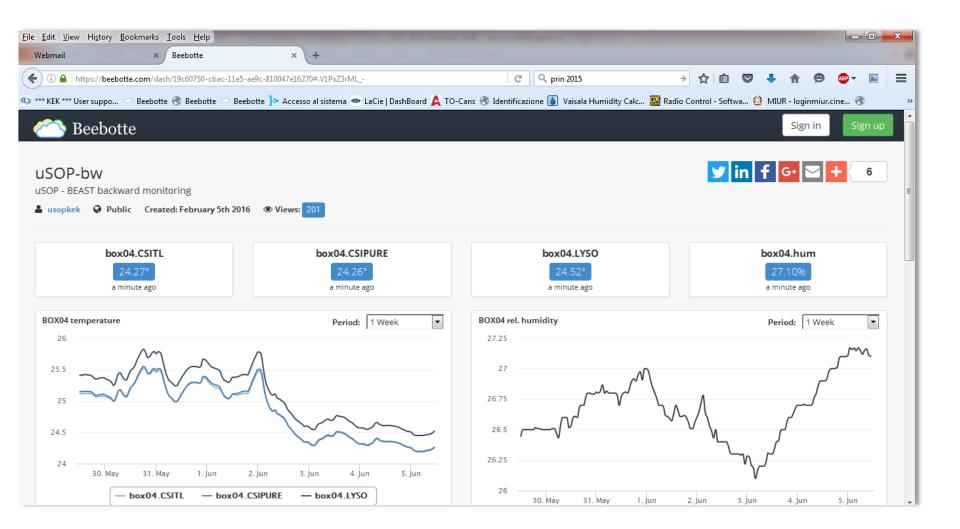

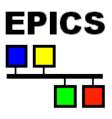

#### Beebotte as EPICS IOC consumer

- Beebotte (<u>https://beebotte.com/</u>) is an open cloud platform for network connected objects

- In our system, EPICS IOCs are interfaced with Beebotte using the bbt-Python library. Data is pushed to Beebotte every few minutes.

- A Publish/Subscribe model offers bidirectional data communication. Users decide which data to retain by using persistent and/or transient messages.

- Beebotte has REST API to let backend (server) applications read, write and publish data.

## System Metrics Dasboard

- In the same fashion,

Beebotte is also used

to monitor the uSOP

main system metrics:

- CPU load

- RAM/FLASH usage

- Network activity

- peripheral power supplies

#### **SLOWDOWN...**

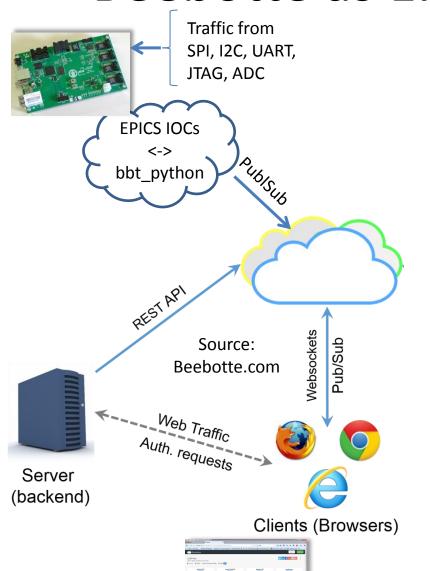

#### $\Delta\Sigma$ ADC – LTC2499 noise floor

- uSOP bench test with LTC2499:

- $-\Delta\Sigma$  ADC, 24 bit

- I<sup>2</sup>C, powered by uSOP isolated supply

- V<sub>in</sub> = 0V, Input shorted to local ground

- ~5 Hz sampling rate

- x1 mode

- 50 Hz filter

- $-V_{ref}:5V$

- Read-out by EPICS IOC

- GUI by CSS/BOY

\_3 -2.4 -1.8 -1.2 -0.6 0

OUTPUT READING (µV)

Source: linear.com

#### uSOP @ BEAST

#### **Beebotte Dashboard**

- BEAST is a detector presently taking data at SuperKEKB Interaction Point, to study beam backgroung

- uSOP is monitoring T and Rh of the 18 BEAST crystals (LYSO, CsI, CsI(Tl). Data available via EPICS and Beebotte

20th IEEE Real Time 2016 - Padua, Italy

uSOP minicrate for BEAST

### The EndCap ECL monitoring system 1/2

uSOP box

EndCap Sectors 7F and 8F

Minimal, standalone monitoring system at the EndCap ECL test station

- 4 sectors over 32 monitored to control the conditioning system (T, Rh)

- Up-time > 1 year

- Data available via both EPICS and cloud

EndCap Test Station at Fuji Exp. Hall, KEK

#### The ECL EndCap monitoring system 2/2

uSOP crate

uSOP 6U unit (internal view)

- The final monitoring system will be installed at KEK during 2016

- Forward and Backward ECL:

- 2112 CsI(Tl) crystals, 32 sectors

- T and Rh monitor, 128 analog channels (96 thermistors + 32 Rh probes)

#### Features:

- 3-wire read-out to cancel the 40m cable stray resistance

- Stray thermocouple effects cancellation

- 8 uSOP boards, 16 ADCs (24 bit)

- 6U, 12HP form factor, shielded

- Selective ground scheme to avoid loops

- Read-out and controls via network

#### IS UNDER DEVELOPMENT...

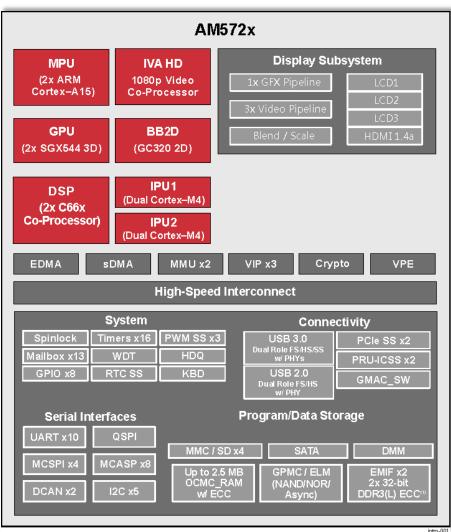

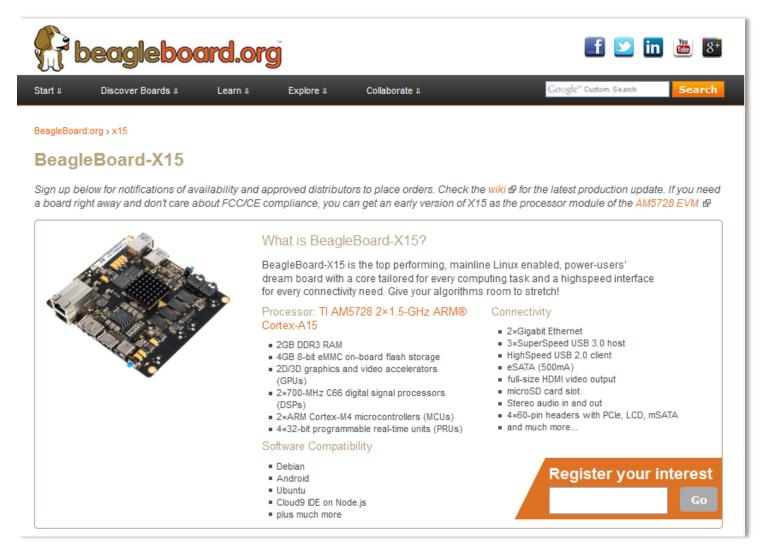

## Going plus...

- Texas Instruments has released recently the 1.5 GHz dual-core Cortex A15 Sitara AM5728

- On this uP, we have started the design of a new platform with FPGA and dual high-speed ADC: uSOP+

- Not just monitoring: DSP, hardware processing, high-speed links, ...

#### Conclusions

- uSOP has been intensively tested at KEK, starting from Apr. 2015

- Stable and reliable LINUX platform, with uptime > 1 year

- Access to SITARA Event Capture peripherals

- Hardware controllers for all most common field busses

- Fully (re)configurable and managed remotely (from brick to fully functional)

- Designed to work as a stand-alone unit, yet easy to deploy in complex control infrastructures

- EPICS and NSMv2 compliant, IOCs developed for all the needed DAQ units

- A last thing for the Manga lovers...

### Just for fun ...

Usop

- Japanese colleagues told us Usop (ウソップ) is one of the *One Piece* characters by the manga writer Eiichiro Oda

- ... More about Usop on wikipedia:

- https://it.wikipedia.org/wiki/Usop

#### **BACKUP**

## Cortex A Cores (32bit)

| Cortex-A<br>(32-bit) | ARMv7-A | Cortex-A5 <sup>[23]</sup>  | Application profile, ARM / Thumb / Thumb-2 / DSP / SIMD / Optional VFPv4-D16 FPU / Optional NEON / Jazelle RCT and DBX, 1–4 cores / optional MPCore, snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP)                                                                                                                                                    | 4-64 KB / 4-64 KB L1, MMU +<br>TrustZone                                                                   | 1.57 DMIPS/MHz per core                                                                            |

|----------------------|---------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                      |         | Cortex-A7 <sup>[24]</sup>  | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4-D16 FPU / NEON / Jazelle RCT and DBX / Hardware virtualization, in-order execution, superscalar, 1–4 SMP cores, MPCore, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP, architecture and feature set are identical to A15, 8-10 stage pipeline, low-power design <sup>[25]</sup> | 8-64 KB / 8-64 KB L1, 0-1 MB L2, MMU<br>+ TrustZone                                                        | 1.9 DMIPS/MHz per core                                                                             |

|                      |         | Cortex-A8 <sup>[26]</sup>  | Application profile, ARM / Thumb / Thumb-2 / VFPv3 FPU / NEON / Jazelle RCT and DAC, 13-stage superscalar pipeline                                                                                                                                                                                                                                                                                     | 16-32 KB / 16-32 KB L1, 0-1 MB L2 opt<br>ECC, MMU + TrustZone                                              | Up to 2000 (2.0 DMIPS/MHz in speed from 600 MHz to greater than 1 GHz)                             |

|                      |         | Cortex-A9 <sup>[27]</sup>  | Application profile, ARM / Thumb / Thumb-2 / DSP / Optional VFPv3 FPU / Optional NEON / Jazelle RCT and DBX, out-of-order speculative issue superscalar, 1–4 SMP cores, MPCore, snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP)                                                                                                                         | 16-64 KB / 16-64 KB L1, 0-8 MB L2<br>opt parity, MMU + TrustZone                                           | 2.5 DMIPS/MHz per core, 10,000 DMIPS<br>@ 2 GHz on Performance Optimized<br>TSMC 40G (dual-core)   |

|                      |         | Cortex-A12 <sup>[28]</sup> | Application profile, ARM / Thumb-2 / DSP / VFPv4 FPU / NEON / Hardware virtualization, out-of-order speculative issue superscalar, 1–4 SMP cores, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP)                                                                                                             | 32-64 KB / 32 KB L1, 256 KB-8 MB L2                                                                        | 3.0 DMIPS/MHz per core                                                                             |

|                      |         | Cortex-A15 <sup>[29]</sup> | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4 FPU / NEON / integer divide / fused MAC / Jazelle RCT / hardware virtualization, out-of-order speculative issue superscalar, 1–4 SMP cores, MPCore, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP, 15-24 stage pipeline[25]                                                     | 32 KB w/parity / 32 KB w/ECC L1,<br>0-4 MB L2, L2 has ECC, MMU +<br>TrustZone                              | At least 3.5 DMIPS/MHz per core (up to 4.01 DMIPS/MHz depending on implementation) <sup>[30]</sup> |

|                      |         | Cortex-A17                 | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4 FPU / NEON / integer divide / fused MAC / Jazelle RCT / hardware virtualization, out-of-order speculative issue superscalar, 1–4 SMP cores, MPCore, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP                                                                               | MMU + TrustZone                                                                                            | ?                                                                                                  |

|                      | ARMv8-A | Cortex-A32 <sup>[31]</sup> | Application profile, AArch32, NEON advanced SIMD                                                                                                                                                                                                                                                                                                                                                       | 8-64 KB w/optional parity / 8-64 KB<br>w/optional ECC L1 per core,<br>128 KB-1 MB L2 w/optional ECC shared |                                                                                                    |

## Beaglebone Black

#### AM5728

AM5728, AM5726 SPRS953 – DECEMBER 2015

#### AM572x Sitara™ Processors Silicon Revision 2.0

#### 1 Device Overview

#### 1.1 Features

- For Silicon Revision 1.1 information, see SPR915

- ARM® Dual Cortex®-A15 Microprocessor Subsystem

- Up to 2 C66x™ Floating-Point VLIW DSP

- Fully Object-Code Compatible With C67x<sup>™</sup> and C64x+<sup>™</sup>

- Up to Thirty-two 16 × 16-Bit Fixed-Point Multiplies per Cycle

- Up to 2.5MB of On-Chip L3 RAM

- Two DDR3/DDR3L Memory Interface (EMIF) Modules

- Supports up to DDR3-1066

- Up to 2GB Supported per EMIF

- Dual ARM® Cortex®-M4 co-processors

- IVA-HD Subsystem

- Display Subsystem

- Full-HD Video (1920 x 1080p, 60 fps)

- Multiple Video Input and Video Output

- 2D and 3D Graphics

- Display Controller With DMA Engine and up to Three Pipelines

- HDMI™ Encoder: HDMI 1.4a and DVI 1.0 Compliant

- 2x Dual-Core Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS)

- 2D-Graphics Accelerator (BB2D) Subsystem

- Vivante™ GC320 Core

- Video Processing Engine (VPE)

- Dual-Core PowerVR® SGX544™ 3D GPU

- Crypto Hardware Accelerators

- AES, SHA, RNG, DES and 3DES

#### . Three Video Input Port (VIP) Modules

- · General-Purpose Memory Controller (GPMC)

- Enhanced Direct Memory Access (EDMA) Controller

- 2-Port Gigabit Ethernet (GMAC)

- · Sixteen 32-Bit General-Purpose Timers

- 32-Bit MPU Watchdog Timer

- Five Inter-Integrated Circuit (I<sup>2</sup>C) Ports

- Five inter-integrated Circuit

HDQ™/1-Wire® Interface

- · Ten Configurable UART/IrDA/CIR Modules

- Four Multichannel Serial Peripheral Interfaces (MCSPIs)

- Quad SPI Interface (QSPI)

- SATA Gen2 Interface

- Multichannel Audio Serial Port (MCASP)

- SuperSpeed USB 3.0 Dual-Role Device

- High-Speed USB 2.0 Dual-Role Device

- PCI-Express® 2.0 Subsystems With Two 5-Gbps Lanes

- One 2-lane Gen2-Compliant Port

- or Two 1-lane Gen2-Compliant Ports

- Dual Controller Area Network (DCAN) Modules

CAN 2.0B Protocol

- Up to 247 General-Purpose I/O (GPIO) Pins

- Power, Reset, and Clock Management

- On-Chip Debug With CTools Technology

- 28-nm CMOS Technology

- 23 mm × 23 mm, 0.8-mm Pitch, 760-Pin BGA (ABC)

# **ADVANCE INFORMATION**

## Beagleboard X15

#### **BEAST** dashboard