# Data Chain Reconstructing Technology for the front-end electronics of the BESIII muon identification system

Jianbo Xi, Xiaoguang Zhang, Shitao Xiang and Hao Liang

Abstract-To reduce the cost and minimize the occupying volume of the transmission cables in the spectrometer, some middle and low energy particle physics experiment employ serial daisy-chain techniques, which organize the front-end cards (FECs) in a daisy-chain topology, and data is transferred in a serial mode from FECs to the rear-end electronics. However, this technique has an obvious limitation in that the failure of a single component will disable the entire data chain. As the only solution, a data chain reconstruction technology is proposed based on the front-end electronics of the Beijing Spectrometer (BESIII) muon identification system. This technology can automatically disconnect malfunctioning front-end cards and reorganize the data transmission channel to minimize the loss of data. In this paper, we report our work on the design of data chain reconstruction, focusing on the realization of data reconstruction using highly reliable anti-fuse field programmable gate arrays (FPGAs), on the prevention of short circuits, and on fault tolerance improvement. A prototype of the reconstructing data chain designed for the front-end electronics of the BESIII muon identification system has fulfilled the requirements of a laboratory environment and is able to now be applied in an actual experiment.

## I. INTRODUCTION

The digitization of front-end electronics for high energy physics experiments has been a trend in recent years. Generally, the readout system of front-end electronics comprises front-end cards (FECs), data transmission cables, photoelectric conversion boards, fibers, and Versa-module Euro (VME) readout boards [1], [2], [3]. To reduce the cost and minimize the occupying volume of the transmission cables in the spectrometer, some small and medium collision experiments in the field of high energy physics employ serial daisy chain techniques, which organize the FECs in a daisy chain topology, and data is transferred in a serial mode from FECs to the rear-end electronics [4], [5]. However, this technique has a substantial shortcoming. If one FEC is damaged, the entire daisy chain will collapse, leading to a blind detector area.

To solve this problem, we have proposed a data chain reconstruction technology for the first time in the world. This technology can automatically disconnect malfunctioning FECs, reorganize the data transmission channel to minimize the loss of data, and reduce the maintenance workload. The proposed data chain reconstruction technology has been

Manuscript received May 29, 2016. This work was supported by the State Key Laboratory of Particle Detection and Electronics of China.

Jianbo Xi, Hao Liang, Xiaoguang Zhang and Shitao Xiang are with State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei, Anhui 230026, P.R. of China (phone: +86-0551-63600387; e-mail: xijb@mail.ustc.edu.cn, zxg@mail.ustc.edu.cn, xst@mail.ustc.edu.cn, simonlh@ustc.edu.cn).

developed based on the front-end electronics of the Beijing Spectrometer (BESIII) muon identification system.

In this paper, we report our work on the design of data chain reconstruction, focusing on the realization of data reconstruction using highly reliable anti-fuse field programmable gate arrays (FPGAs), on the prevention of short circuits, and on fault tolerance improvement. A prototype of the reconstructing data chain designed for the front-end electronics of the BESIII muon identification system has fulfilled the requirements of a laboratory environment and is able to now be applied in an actual experiment.

# II. THE DATA CHAIN STRUCTURE

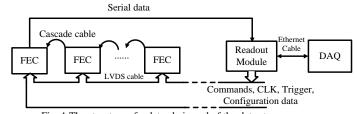

The readout electronics for the BESIII muon identification system is comprised of 40 data chains [6]. The structure of a data chain and of the data stream is illustrated in Fig. 1. Each data chain consists of 16 FECs, which are connected in daisy chain mode via cascade cables. The tasks of the FECs are to transform the information from Resistive Plate Chamber (RPC) strips into digital data, handle the data of the event after the trigger signal, store the data into the sub-event buffers with the appropriate header and wait for the call by the Data Acquisition (DAQ) system. The output of each FEC is a 16-bit serial stream and is connected to the next FEC in daisy chain mode. At the end of the data chain (far left in the figure), the data from all 16 FECs' are converted into the low voltage differential signaling (LVDS) format and transmitted to the readout module through a 30m long shielded twisted pair cable by the final FEC. Control commands, clocks, triggers and configuration data are also transmitted via this cable.

Fig. 1 The structure of a data chain and of the data stream

# III. FEC DESIGN

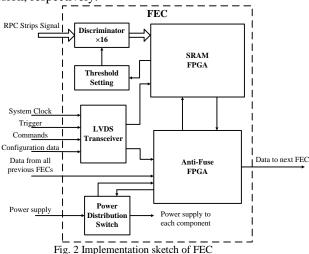

The original FEC design is modified to achieve a data chain reconstruction function. The new designed FEC uses a SDRAM based on FPGA (SF) and an anti-fuse based FPGA (AF), which carry out all the logical functions required for processing digital data. Fig. 2 shows an implementation sketch of the FEC. Besides the FPGAs, four other types of components are adopted for different tasks [7]. The discriminator component, whose threshold level is set by the threshold setting circuit, performs signal detection. The

power-distribution switch and the LVDS transceiver components are responsible for the power supply monitoring and control of each component and the electric level conversion, respectively.

## A. FPGA logics

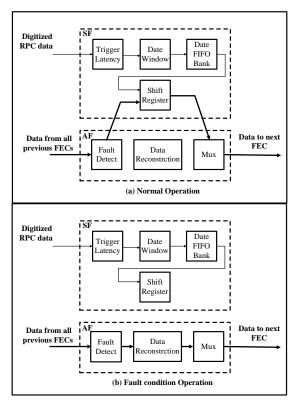

The Actel AM series anti-fuse FPGA was chosen as the AF, which provides several benefits such as high reliability and live at power-up capability, with no secondary support components required, along with increased tolerance to certain radiation effects [8]. Due to its very high reliability and stability, the AF is very difficult to damage. In this premise, Fig. 3 displays the general operational diagram of the data processing logic.

Under the normal operation conditions, as shown in Fig.3 (a), the digitized RPC data coming from 16 channels are stored in the FIFOs of SF waiting for the trigger signal. The output of the shift registers become a 16-bit serial stream and connected to the data from all previous FECs when the trigger signal occurs. The AF just supplies a data path for the serial chain data.

When a fault occurs in a certain FEC, the power supply of this FEC is cut off except for the AF. In this case, as shown in Fig.3 (b), the fault detection module of AF is commanded to output data to the data reconstruction module, in which data losses of the RPC information is compensated by bits "0" and fault flag in order to keep consistent with the data format of the normal operation conditions.

Fig. 3 The operational diagram of the data processing logic

## B. Power monitor and control

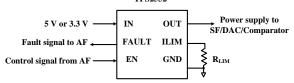

As for the data chains installed inside a detector, the environment around a FEC can be so adverse that any fault condition is possible, even short circuits [9]. Once a short circuit is encountered in a particular FEC, the normal operation of the entire data chain may be permanently disrupted. To solve this problem we employ the TPS2552 current-limit power-distribution switch (TI Corporation), which can limit the output current to a safe level and automatically cut off the power supply with the assertion of a fault signal in response to a short circuit. The application schematic diagram is shown in Fig. 4.

Fig. 4 The application schematic diagram of the power-distribution switch

# C. Redundancy design

Finally, to improve the fault tolerance, some redundancy hardware is designed, including a redundancy power supply for the AF and the LVDS transmitter chips.

# IV. TESTS

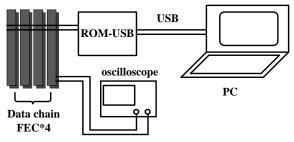

Specific tests were conducted to validate the feasibility and reliability of the proposed hardware scheme in a laboratory environment. As illustrated in Fig. 5, the experimental setup consisted of four FECs, a USB-based readout module (ROM-

USB), and a computer. The ROM-USB is mainly used to simulate the VME module, which provides clock, trigger, command and self-test data to the FECs to test their performance.

Fig. 5 Experimental test platform setup

## A. Normal work mode test

The normal work mode test employed a trigger rate of 1 k Hz corresponding to the threshold of 40 mV, and no data lost or error in a 24-hour test period [10].

#### B. Abnormal work mode test

In the abnormal work mode test, the power supply for SF as well as comparators and the DAC were cut off to simulate a condition of damage. Four tests under different conditions were carried out, as listed in Table I. The results indicated that the data chain achieved the data reconstruction function as expected, as shown by the following.

- a) The normal work mode FECs performed well with no data lost or errors incurred.

- b) The data format did not change compared with normal work mode.

- c) The data for breakdown FECs were "0", which do not influence the detector hit count histogram.

TABLE I ABNORMAL WORK MODE TEST CONDITIONS

#### C. Short circuit test

In this test, a short circuit was artificially introduced into a normally functioning data chain to determine whether the

|       | First FEC | FEC2      | FEC3      | Last FEC  |

|-------|-----------|-----------|-----------|-----------|

| Test1 | Virtually | Normal    | Normal    | Normal    |

|       | damaged   |           |           |           |

| Test2 | Virtually | Virtually | Virtually | Normal    |

|       | damaged   | damaged   | damaged   |           |

| Test3 | Normal    | Virtually | Normal    | Virtually |

|       |           | damaged   |           | damaged   |

| Test4 | Normal    | Virtually | Virtually | Virtually |

|       |           | damaged   | damaged   | damaged   |

power-distribution switches were able to cut-off the power in a timely fashion and provide an assertion of a fault signal to the anti-fuse FPGA. The result indicated that the power was cut off within 10 ms after the short circuit occurred and an alarm signal was sent to the anti-fuse FPGA to notice which to performance data reconstruction function.

#### V. CONCLUSION

In this paper, a latest data chain reconstruction technology was presented. The technology, which is proposed for the first time in the world, provides automatic disconnection of malfunctioning boards and data reconstruction functions to minimize data loss. This method is proposed and developed based on the front-end electronics of the BESIII muon identification system. Test results indicate that the design is feasible and reliable and it will be applied in the future to an actual BESIII experiment.

#### REFERENCES

- ALICE Collaboration, TDR of the Muon Spectrometer, CERN/LHCC 99-22, 1999.; Spegel M, Nucl Instrum Meth Phys Res A, 2000 453: 308-314

- [2] ATLAS Muon Collaboration, ATLAS Muon Technical Design Report, CERN/ LHCC 97-22, 1997.

- [3] CMS Collaboration, Muon Project, CERN/LHCC 97-32, 1997

- [4] BaBar, Technical Design Report, SLAC-R-457, March 1995.; Aubert B, Bazan A, Boucham A, et al, et al. Nucl Instrum Meth Phys Res A, 2002 479: 1-116.

- [5] BELLE Collaboration, A study of CP violation in B meson decays, Technical Design Report, KEK Report 95-1, April 1995.;

- [6] Zhang J, Qian S, Chen J, et al. Nucl Instrum Meth Phys Res A, 2010 614: 195-205.

- [7] Yang H, Liang H, Yuan Y, et et al. IEEE Trans Nucl Sci, 2010 57: 2371-2371

- 8] Qin X, Feng C, Zhang D, et al. Nul Sci Tech, 2013 24: 040403-040403.

- [9] Xi J, Liang H, Xiang S , et al. Nul Sci Tech, 2014 25: 020404-020404.

- [10] Hao H, Liang H, Zheng L, et al. Nul Sci Tech, 2013 24: 010401-010401