# THE ASSOCIATIVE MEMORY SYSTEM INFRASTRUCTURE OF THE ATLAS FAST TRACKER

20th Real Time Conference, 5-10 June 2016, Padova, Italy

# **OVERVIEW**

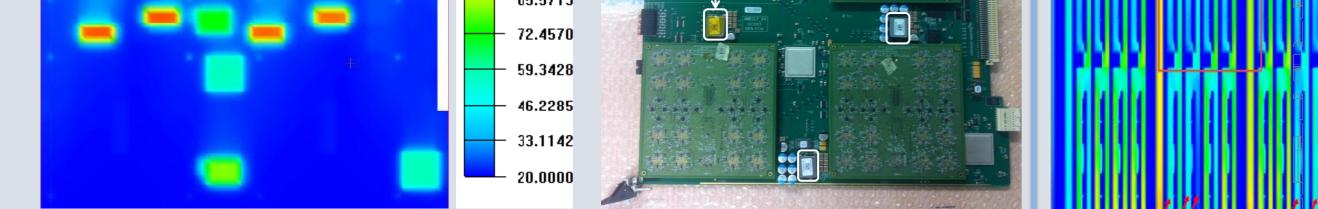

The FTK [1] is designed to perform pattern matching of detector channels hit by charged particles crossing the ATLAS experiment [2] sillicon tracker. The Associative Memory (AM) [3] system of the Fast TracKer processor has been designed is the main processing element of FTK and is based on the use of ASICs designed to execute pattern matching with a high degree of parallelism. It finds track candidates at coarse resolution that are seeds for higher precision track fitting. The AM system implementation is a collection of 128 boards, named "Serial Link Processors" (AMBSLPs) [4]. On these boards a huge traffic of data is implemented on a network of 900 2 Gb/s serial links. Even if the complete AM-based processor is much less power consuming (~40 kW) than its CPU equivalent, its size is much smaller. The result is an extremely high consumption per unit volume and the need for complex custom infrastructures in order to have a correct cooling. The AMBSLP has a consumption of ~250 W.

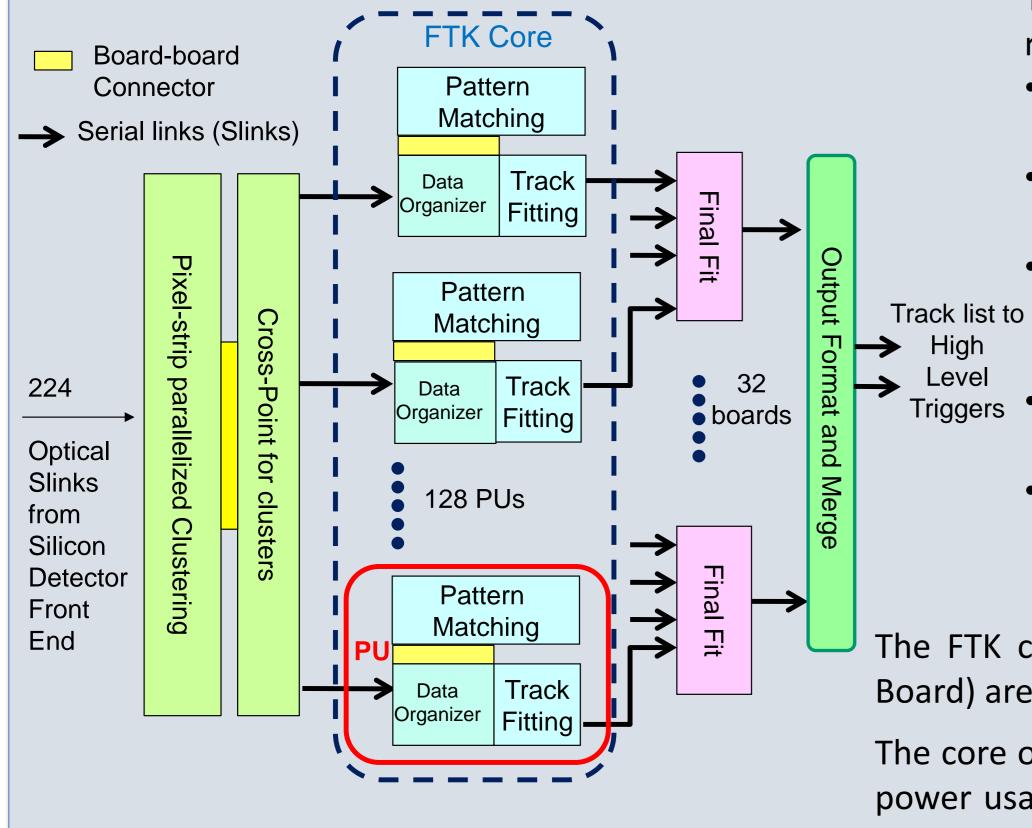

## **FTK ARCHITECTURE**

The FTK core solves the huge combinatorics

# FTK PROCESSING UNIT (PU)

- required by pattern recognition.

- is the most power and timing consuming part of FTK.

- Organized into **128 Processing Units** (PUs) which process the tracker data in parallel

- Each PU executes in pipeline the two main FTK algorithms, the Pattern Matching (PM) and the Track Fitting (TF). Data Organizer is the interface between the two algorithms

- Final Fit uses 4 additional SCT layers to remove even more fake tracks

The FTK core along with the Final Fit (Second Stage Board) are located on VME bins.

The core of FTK is compact (4 racks of electronics) and power usage is low (~50 kW) if compared to the farm of thousands of commercial CPUs [5] required to perform an equivalent task.

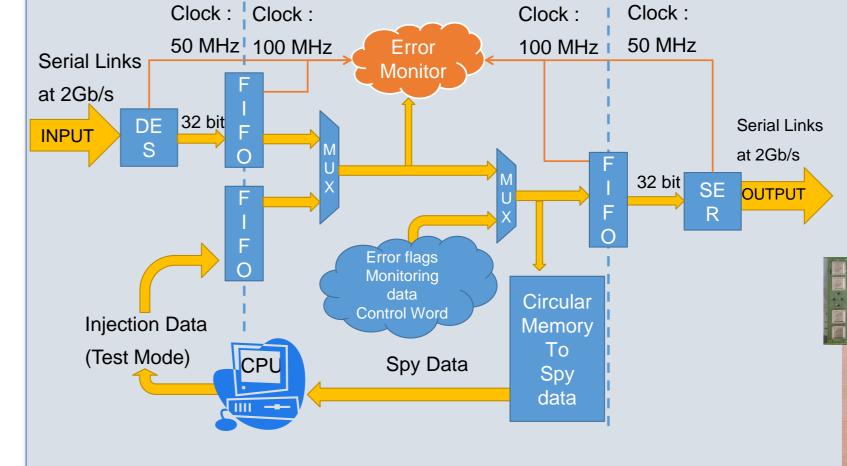

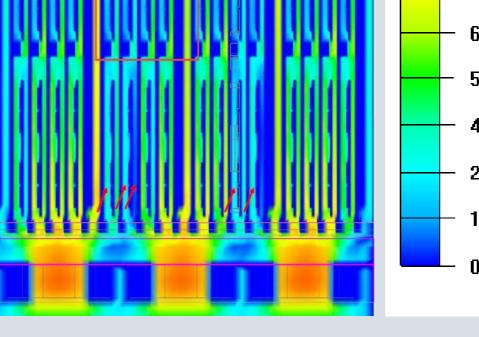

On the left: Representation of the data driven pipeline for a single data link inside the AMBSLP. Both input and output FPGA logic is controlled by the external CPU

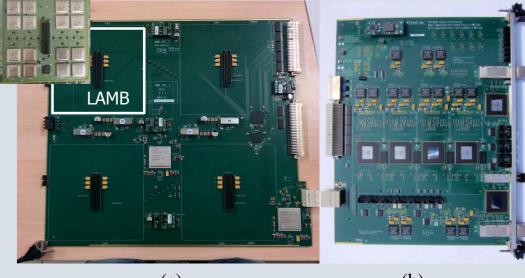

#### Below: The FTK PU

FTK PU consists of:

a) The **AMBSLP** (version 2)

- Each AMBSLP has **4 LAMBs** mounted as mezzanines

- Each LAMB contains **16 AM chips** that perform Pattern Matching

- On the board there are 5 General Electric DC-DC converters that distribute the 48V input to the LAMBs, keeping the power as high as possible

b) AUXiliary Card which contains the Data Organizer and the Track Fitter

PU's average power consumption is 250W (AMBSLP) + 80W(AUX)

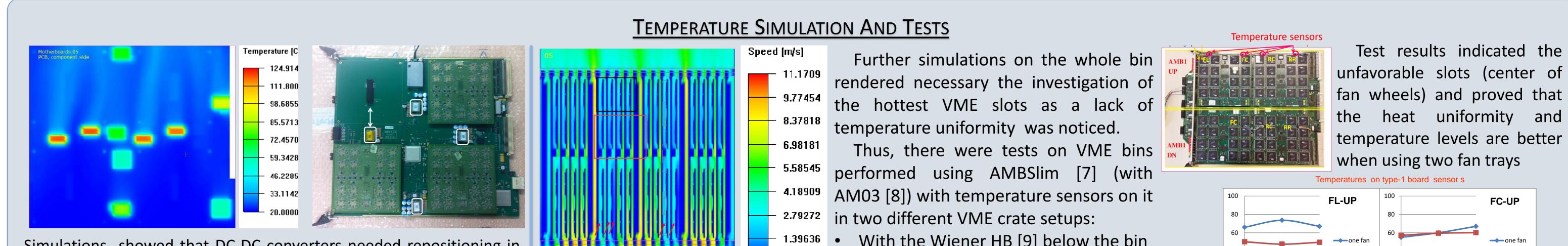

Simulations showed that DC-DC converters needed repositioning in order to improve thermal state of the upper LAMBs. PCB temperature could reach ~90°C and the AM chip some degrees more

911

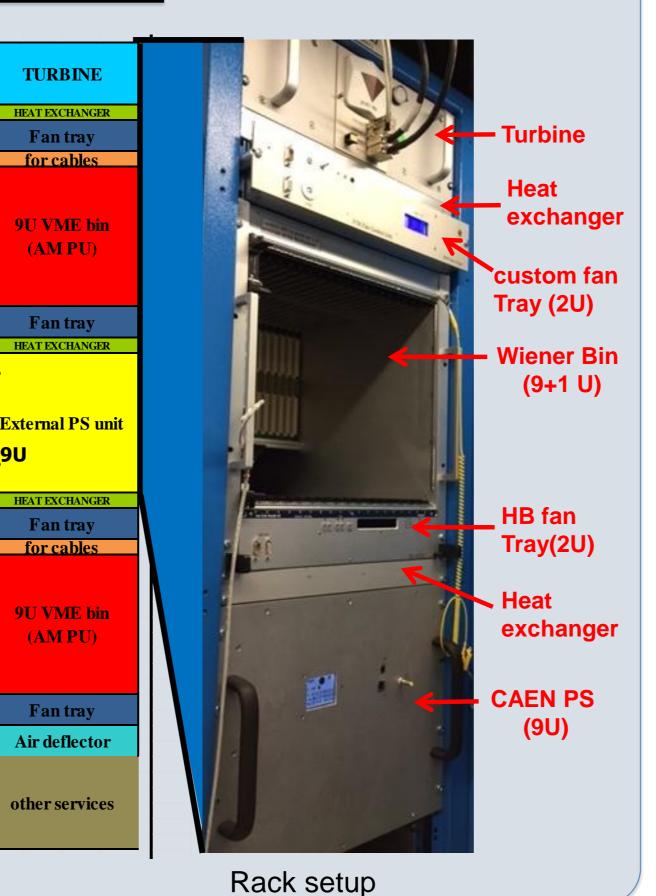

With the Wiener HB [9] below the bin With two fan trays (up and down) 0.000000

**Custom CAEN PS**

### THE AM SYSTEM CUSTOM DESIGNED INFRASTRUCTURES

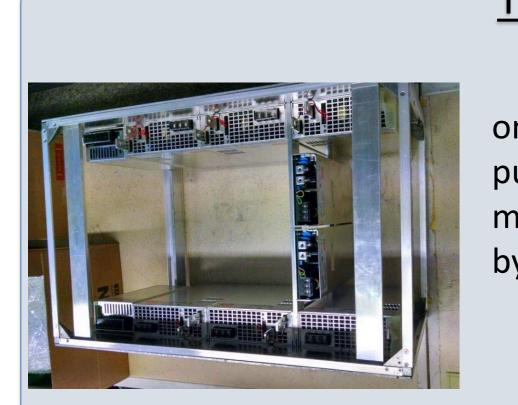

Cooling tests showed that extra cooling on the VME bins was imperative. For this purpose, two Arduino-controlled custommade fan trays were designed and produced by INFN Pavia.

Because of the extra fan trays, space in the rack proved to be an issue. So a custommade power supply by CAEN [6] was designed, able to provide power to two VME bins and their cooling systems and at the same time save enough space to even place extra heat exchangers.

# **DETECTOR CONTROL SYSTEM (DCS)**

Slot #

The fact that the AM System Infrastructure contains custom designed parts proved to be a challenge as well for the development of the FTK DCS. It introduced as new a Simple Network Management Protocol (SNMP) communication between Arduino and PC for the custom fan trays and an OPC UA Server that runs on the VME Single Board Computer (SBC) to monitor all the VME boards

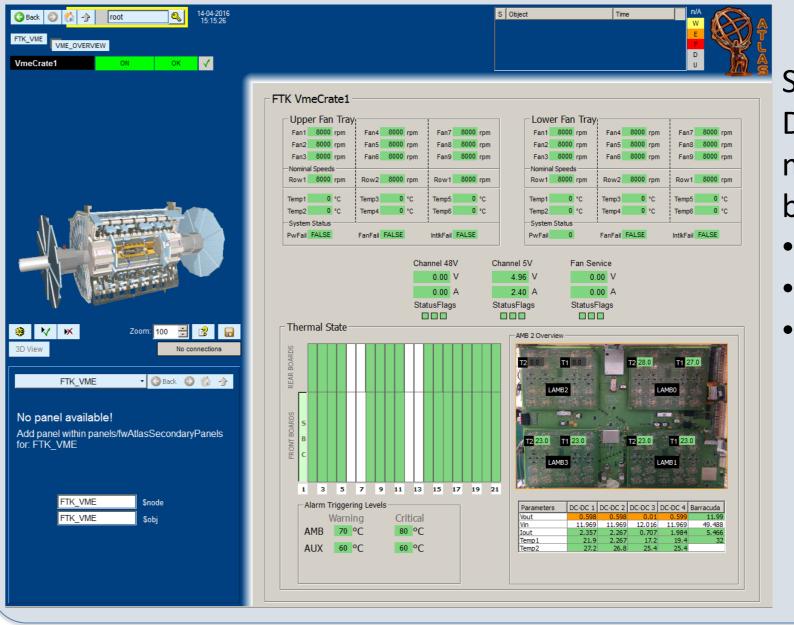

Screenshot of the FTK VME DCS project in Lab4. In the main panel from top to bottom:

Slot #

- Fan tray monitor

- CAEN PS monitor

- VME boards monitor

# REFERENCES

- 1) ATLAS Collaboration., "The Fast Tracker (FTK) Techinical Design Report" CERN-LHCC-2013-007; ATLAS-TDR-021; available online: https://cds.cern.ch/record/1552953

- The ATLAS Collaboration, "The ATLAS Experiment at the CERN Large Hadron Collider," Journal of Instrumentation 3 S08003, 2008.

- 3) M. Dell'Orso and L. Ristori, "VLSI Structures Track Finding", Nucl. Instr. and Meth. A, vol. 278, pp. 436-440, 1989.

- 4) S. Citraro et al., "Highly Parallelized Pattern Matching Hardware for Fast Tracking at Hadron Colliders", submitted to IEEE Trans. on Nuclear Science, October 2015.

- The CMS Collaboration, "Description and performance of track and primary-vertex reconstruction with the CMS tracker", Journal of Instrumentation 9 P10009, 2014.

- CAEN Costruzioni Apparecchiature Elettroniche Nucleari S.p.A., Via Vetraia, 11 55049 Viareggio (LU) Italy

- 7) G. Batignani, et al., The associative memory for the self-triggered SLIM5 silicon telescope, in: IEEE Nuclear Science Symposium, conference record, Dresden, Germany, October 19-25 2008, pp. 2765-2769.

- 8) A. Annovi, et al., "VLSI Processor for Fast Track Finding Based on Content Addressable Memories", in IEEE Trans. on Nuclear Science, vol. 53, no. 4, pp. 2428-2433, August 2006.

- 9) Worldwide-Industrial Electronics-Nuclear Electronics-Resource W-IE-NE-R, Plein & Baus GmbH Linde 18 D 51399 Burscheid Germany www.wiener-d.com

# ACKNOWLEDGEMENTS

This work receives support from Istituto Nazionale di Fisica Nucleare; The project has received funding from the European Union's Seventh Framework Programme for research, technological development and demonstration under grant agreement n.324318. This work has received funding from the State Scholarships Foundation of Greece (IKY)