# A Testbench Based on UVM Research for ABCStar

Libo Cheng<sup>1</sup>, Francis Anghinolfi<sup>2</sup>, Ke Wang<sup>1</sup>, Zhen-An Liu<sup>1</sup>, Hongbo Zhu<sup>1</sup>, Weiguo Lu<sup>1</sup>

1, Institute of High Energy Physics, CAS, Beijing 100049, China

## 2, CERN, Geneve CH-1211, Switzerland

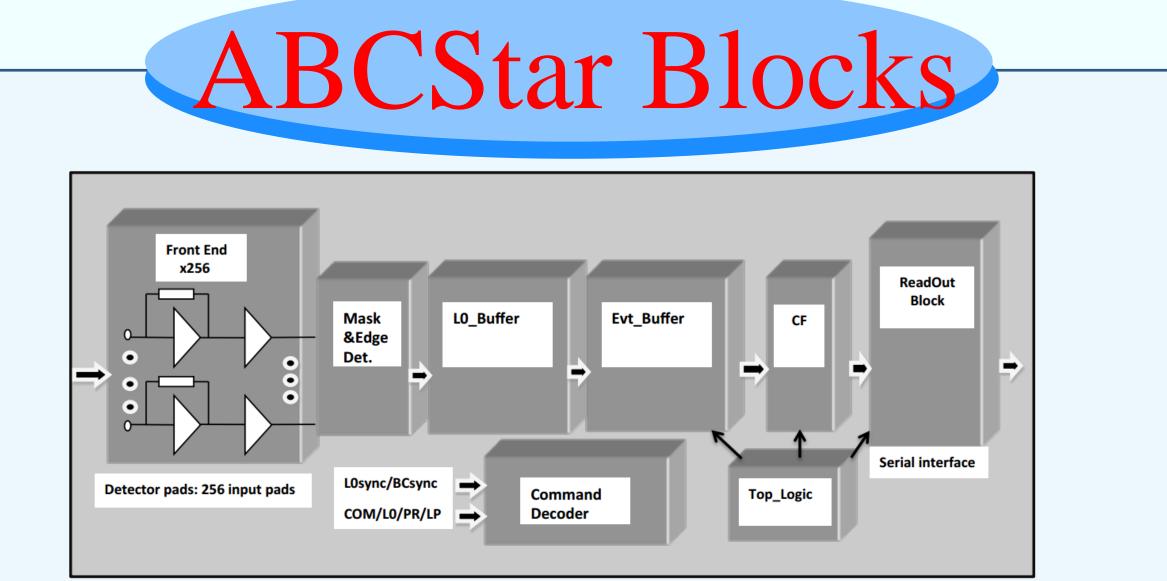

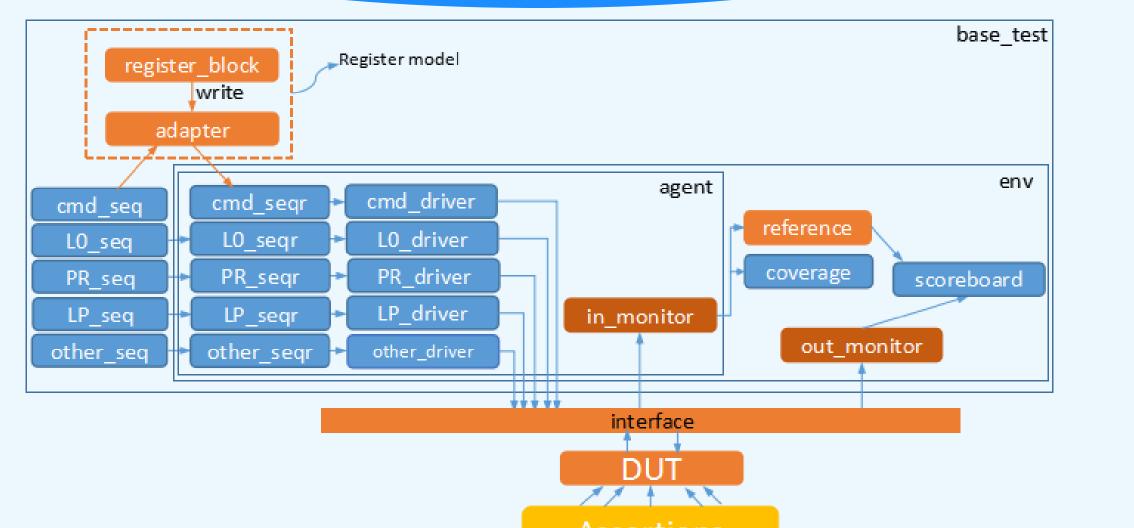

It is demanding to implement more and more functions and algorithms in front-end Application-Specific Integrated Circuit (ASIC), which, in consequence, makes the logic designs more complicated. It necessitates to develop reliable and robust function verification test benches during ASIC designs. ABCStar is a front-end readout ASIC under development and aims to read out the silicon strip sensor for ATLAS Phase II upgrade. Its digital part would include two levels of buffering, several trigger modes, cluster identification, data formatting, and etc. To simulate and verify its full functions, we have built a well-constructed testbench with the Universal Verification Methodology (UVM), which represents an advance and powerful verification methodology based on SystemVerilog. Features of the testbench include: functional coverage evaluation, result comparison with reference models, and selected SystemVerilog assertions for validating key design features.

pip ThreeBC hit ass

LO Pipeline as:

cket compare

) tstprinBCIDmod\_ass |assert|

pulsetestmod ass

### 1 Input Register detection mode test

There are four detection modes for ABCStar Input Register, two for normal data taking (Level and Edge mode), one for alignment (hit mode), and one reserved for special usage.

With corresponding concurrent assertions, we can check whether the Device Under Test (DUT) works correctly in each mode. We also sample the functional coverage output hits of the Input Register in three modes,

LOL1\_assertion |top.dut.abcstar\_dut.LOL1\_dut.pipeline

InReg assertion top.dut.abcstar\_dut.RegIn\_dut.InReg

InReg\_assertion|top.dut.abcstar\_dut.RegIn\_dut.InReg

InReg\_assertion\_top.dut.abcstar\_dut.RegIn\_dut.InReg

Finished | Failed

20143

Count 📫 Count Count

finished inactive

inactive

inactive

finished

inactive

inactive

inactive

oreboard.main phase.packet comp

| 300 <b>-</b>            | į     | nReg<br>' | g out | put o  | chan  | nels             | cour             | ntst:<br>'  | atisti<br>' | c for       | thre          | e de | tecti | on n  | node   | s,       | - 27  |

|-------------------------|-------|-----------|-------|--------|-------|------------------|------------------|-------------|-------------|-------------|---------------|------|-------|-------|--------|----------|-------|

| 300 -<br>200 -<br>100 - | LUMP  | al-       |       | ni. ji | L.    |                  | alle all         | له بله و    | line.       | li.         |               |      | J.    | -     | a kiba | <b>.</b> |       |

| 100                     |       |           |       |        |       |                  |                  |             |             |             |               |      |       |       |        |          |       |

| 0                       | 15    | 30        | 45    | 60     | 75    | 90               | 105              | 120         | 135         | 150         | 165           | 180  | 195   | 210   | 225    | 24       | 0 255 |

| <sup>300</sup> [        | 1     | 1         | 9     | 2      | 10    | 1                | 3                | 9           | 2           |             | P             | ä    | 1     | - 1   | 2      | - E      |       |

| 200 -<br>100            | hal]. | a.D.      | ar p  | at l   | 414.3 | Lr.              | Ъ <sub>Р</sub> - | <b>N</b> M  | l.,         | (phril      | <b> 11-11</b> |      | h     | bel.  | (hal)  | νų.      | hle   |

| 0                       | 15    | 30        | 45    | 60     | 75    | 90               | 105              | 120         | 135         | 150         | 165           | 180  | 195   | 210   | 225    | 24       | 0 255 |

| <sup>600</sup> [        | 12    | - 1       | - 1   | - 21   | 12    | 12               | - 1              | - 1         |             | 12          | 12            | - ar | 21    | ा     | - 21   | T        |       |

| 600<br>400<br>200       | Чł,   | 1 ml      | IJ    |        | կթ    | L <sub>I</sub> n | 16               | l.,         |             | ,jµ.)       | Jh.           | 1-1  | yla   | al lu | n.h    | r l      | 41    |

| 0                       | 15    | 30        | 45    | 60     | 75    | 90               | 105<br>cha       | 120<br>nnel | 135<br>num  | 150<br>Iber | 165           | 180  | 195   | 210   | 225    | 24       | 0 255 |

0 15 30 45

9

ABCStar supports turning off bad or noisy channels through a mask register according to the following logic:

output\_data(256 bits) = input\_data(256 bits) & maskbits(256 bits).

| maskbits&stripdata channels hits statistic                                                          | Assertion Name          | Туре   | Cov | Module/Unit     | Instance                                                      | Current<br>State | Disabled<br>Count | Finished<br>Count | Failed<br>Count |

|-----------------------------------------------------------------------------------------------------|-------------------------|--------|-----|-----------------|---------------------------------------------------------------|------------------|-------------------|-------------------|-----------------|

|                                                                                                     | pip_ThreeBC_lev_ass     | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | finished         | 0                 | 29660             | 0               |

|                                                                                                     | pip_datatakingmod_ass   | assert |     | InReg_assertion | top.dut.abcstar_dut.Regin_dut.inReg                           | finished         | 0                 | 29189             | 0               |

|                                                                                                     | pip_ThreeBC_hit_ass     | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 316               | 0               |

| والمتعلقان والحاز الأراسا المتلك المغربة بالمتحال المتحاد المتحاد المتحاد والمتحاد المتحاد والمتحاد | packet_compare          | assert |     | packet_compare  | worklib.abcstar_uvm_pkg::scoreboard.main_phase.packet_compare | finished         | 0                 | 11                | 0               |

|                                                                                                     | LO_Pipeline_ass         | assert |     | LOL1_assertion  | top.dut.abcstar_dut.LOL1_dut.pipeline                         | inactive         | 0                 | 11                | 0               |

|                                                                                                     | pip_ThreeBC_edge_ass    | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 0                 | 0               |

| 5 60 75 90 105 120 135 150 165 180 195 210 225 240 255                                              | pip_tstprinBCIDmod_ass  | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | o                 | 0               |

| channel number                                                                                      | pip_pulsetestmod_ass    | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | o                 | 0               |

|                                                                                                     | pip_loadmaskbitsmod_ass | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 0                 | 0               |

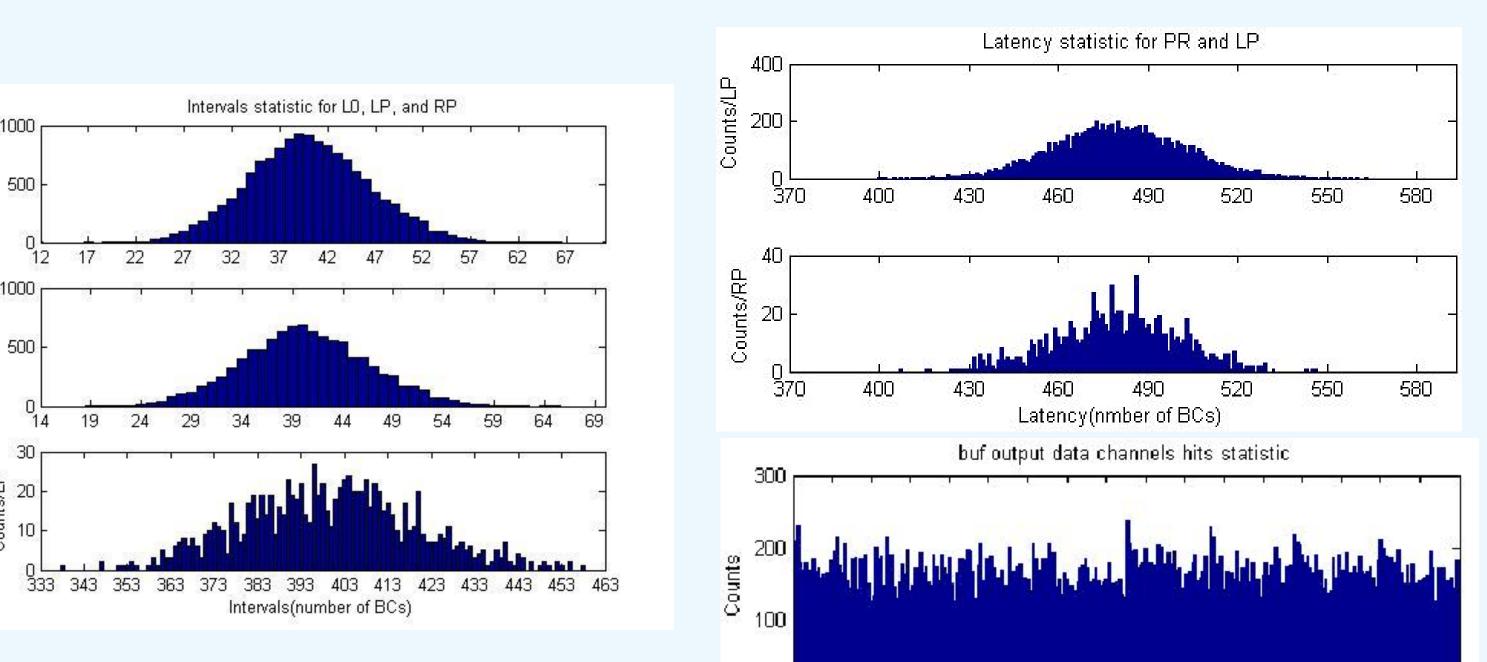

#### 3 Trigger combination test

We use constraint randomized stimulus to produce: L0 with a fixed latency;

Main functions in the digital part:

- $\geq$  256-channel inputs with mask and edge detection functions;

- Three trigger data flow controls: L0, PR, and LP;

- $\succ$  To find clusters and read out them in data packets.

- > Chip reset and internal register configuration by commands.

L0\_intervals = \$dist\_possion(seed, 40)(BCs, rate is 1MHz).LP\_latency=\$dist\_poisson(seed, 480)(BCs, mean is 12us).LP\_intervals =\$dist\_possion(seed, 40)(BCs, rate is 1MHz).PR\_latency=\$dist\_poisson(seed, 480)(BCs, mean is 12us).PR\_intervals =\$dist\_possion(seed, 480)(BCs, mean is 12us).PR\_intervals =\$dist\_possion(seed, 400)(BCs, rate is 100KHz).

\*Note: BC is Beam Crossing Clock, 1BC=25ns

#### Main features:

#### Assertions

- Five independent sequence paths to generate stimulus;

One register model for all commands;

- > One reference model built with combined C and

- SystemVerilog languages;

- ➢ Coverage for functional statistic, and concurrent assertions for realtime validation.

| Assertion Name              | Туре   | Cov | Module/Unit     | Instance                                                      | Current<br>State | Disabled<br>Count | Finished<br>Count | Failed<br>Count |

|-----------------------------|--------|-----|-----------------|---------------------------------------------------------------|------------------|-------------------|-------------------|-----------------|

| pip_datatakingmod_ass       | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | finished         | 0                 | 563025            | 0               |

| pip_ThreeBC_lev_ass         | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | finished         | 0                 | 562703            | 0               |

| LO_Pipeline_ass             | assert |     | LOL1_assertion  | top.dut.abcstar_dut.LOL1_dut.pipeline                         | inactive         | 0                 | 14026             | 0               |

| <br>packet_compare          | assert |     | packet_compare  | worklib.abcstar_uvm_pkg::scoreboard.main_phase.packet_compare | finished         | 0                 | 11000             | 0               |

| pip_ThreeBC_hit_ass         | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 316               | 0               |

| pip_ThreeBC_edge_ass        | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 0                 | 0               |

| <br>pip_tstprinBCIDmod_ass  | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 0                 | 0               |

| <br>pip_pulsetestmod_ass    | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | Ū                 | 0               |

| <br>pip_loadmaskbitsmod_ass | assert |     | InReg_assertion | top.dut.abcstar_dut.RegIn_dut.InReg                           | inactive         | 0                 | 0                 | 0               |

• We have built a well-structured testbench for the ABCStar design based on UVM. It includes functional coverage statistic, a reference for result comparison, and assertions for real time validation.

• We have verified the main features of the ABCStar, by using UVM-constrained and randomized stimulus to simulate the real data input. the coverage and assertions show the design is working correctly.

15 30 45 60 75 90 105 120 135 150 165 180 195 210 225 240 25

hannel number