A. Gianoli<sup>\*</sup> INFN Ferrara on behalf of the GTK group \*CERN, INFN Ferrara, INFN Torino, UCL Louvain

# The M62 & GigaTracker detector

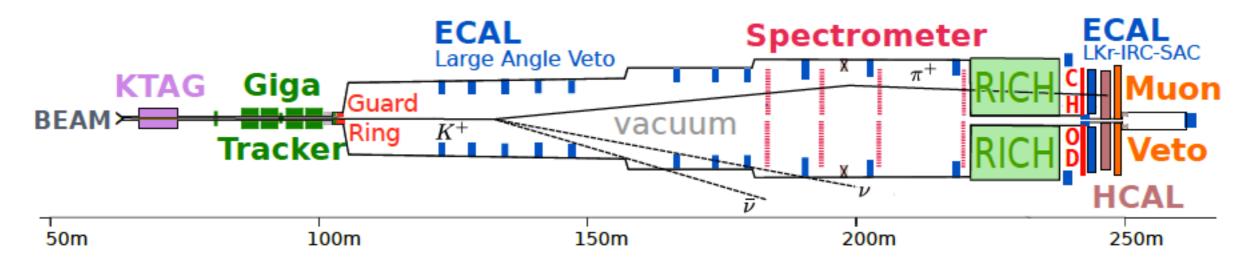

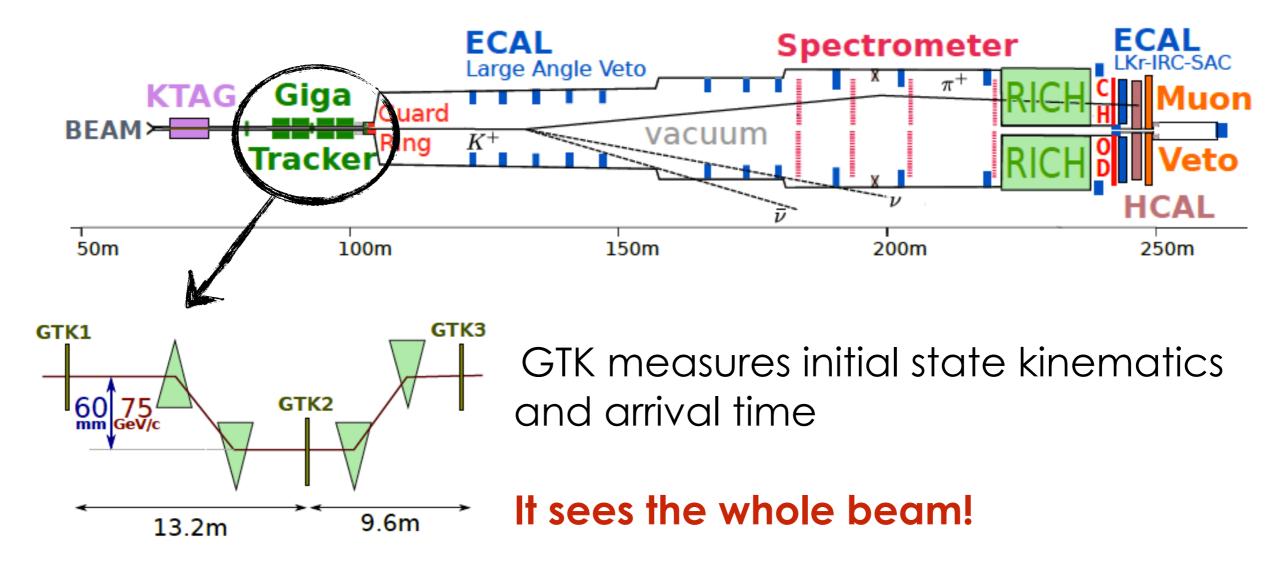

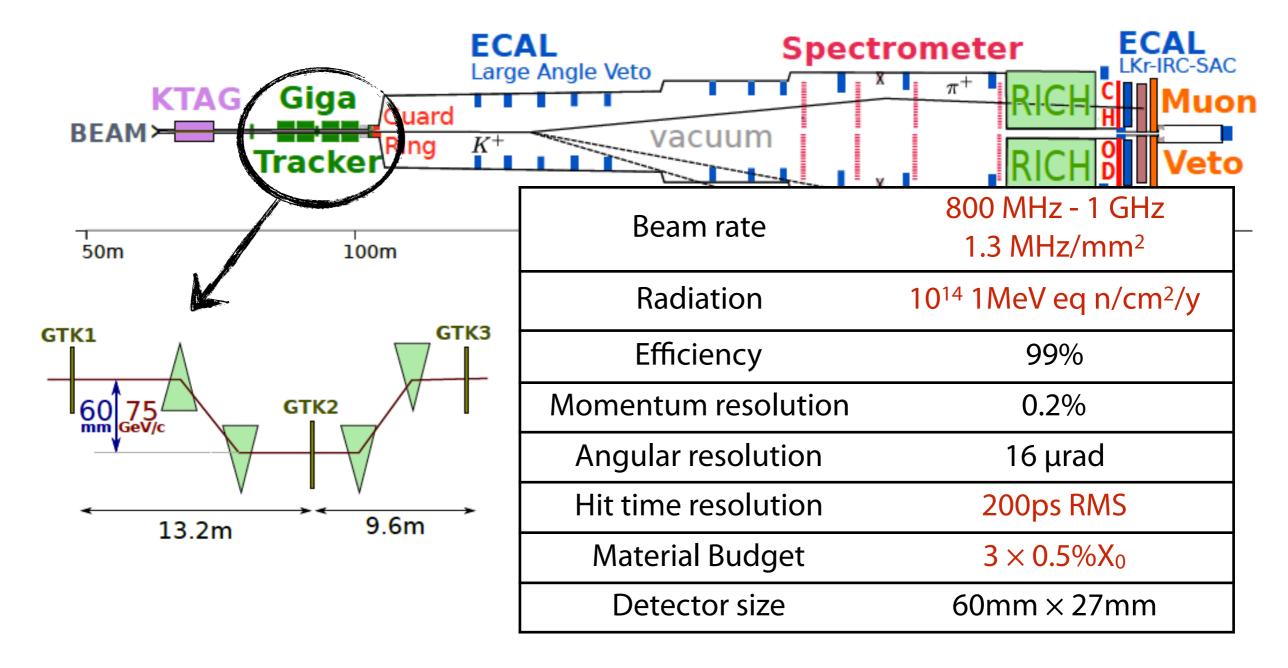

# The NA62 experiment

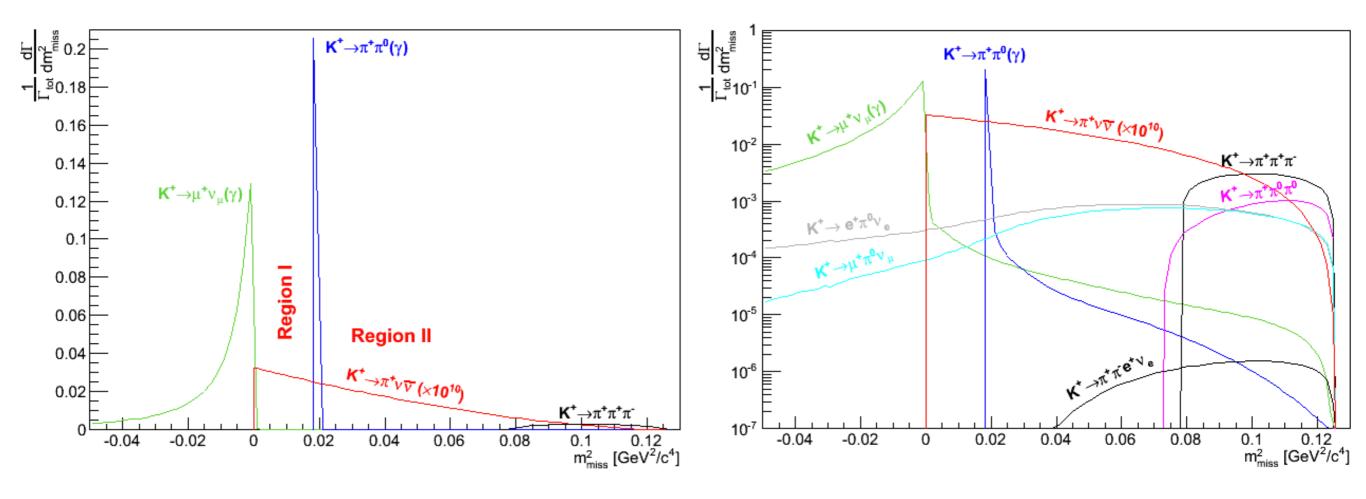

Fixed target experiment: precision kaon physics @Cern SPS Ultra rare K decays  $K^+ \rightarrow \pi^+ \nu \overline{\nu}$ How rare is it? **1 in 10<sup>10</sup>-10<sup>11</sup> particle decays** Aim to get O(100) events in 2-3 years

# The NA62 experiment

Fixed target experiment: precision kaon physics @Cern SPS Ultra rare K decays  $K^+ \rightarrow \pi^+ \nu \overline{\nu}$ How rare is it? **1 in 10<sup>10</sup>-10<sup>11</sup> particle decays** Aim to get O(100) events in 2-3 years

# The NA62 experiment

Fixed target experiment: precision kaon physics @Cern SPS Ultra rare K decays  $K^+ \rightarrow \pi^+ \nu \overline{\nu}$ How rare is it? **1 in 10<sup>10</sup>-10<sup>11</sup> particle decays** Aim to get O(100) events in 2-3 years

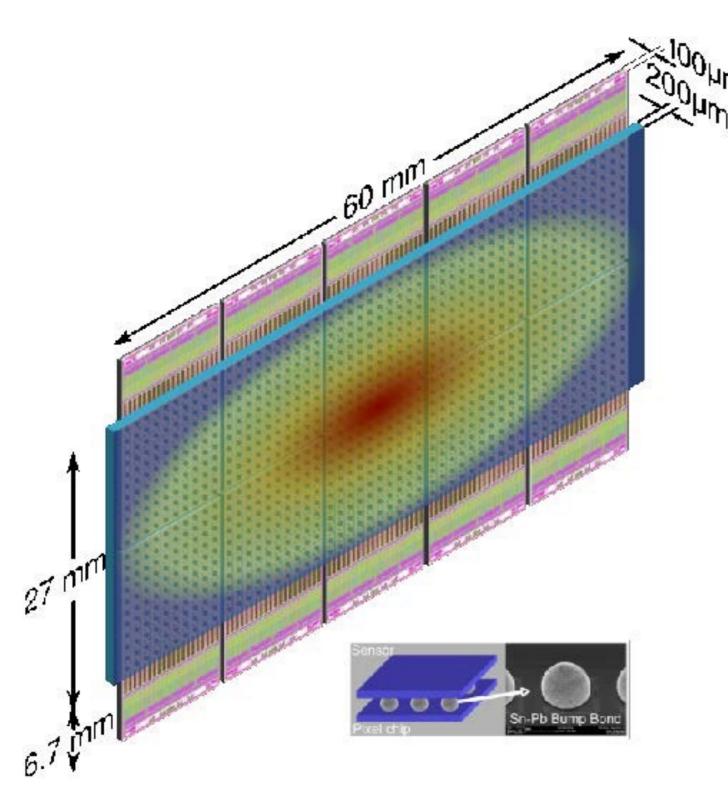

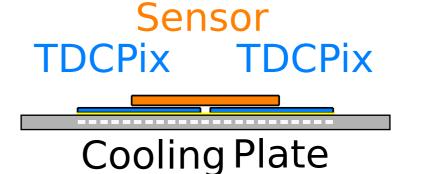

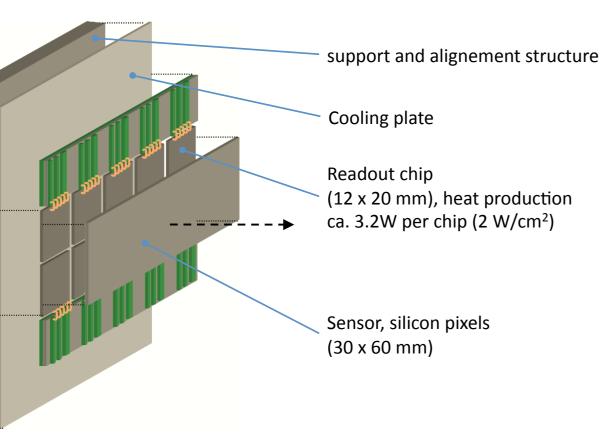

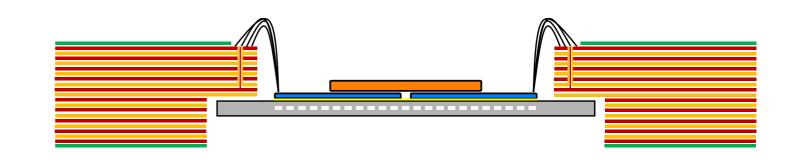

# Sensor-Chip Assembly

Sensor [FBK,CIS] Both p-in-n/n-in-p Bias: 300 - 600 V Thickness: 200 µm MPV Charge per MIP: 2.4 fC

Bump-bonding Sn-PB [IZM]

- ▶ 10 TDCPix chips/station: 130 nm CMOS [IBM] thinned at 100 µm

- Detector replaced every 100 days of beam (radiation)

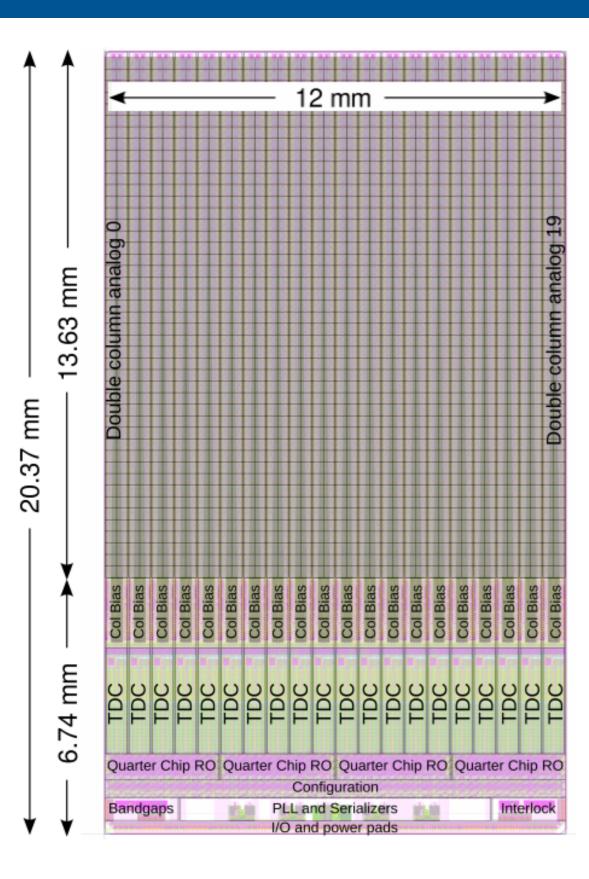

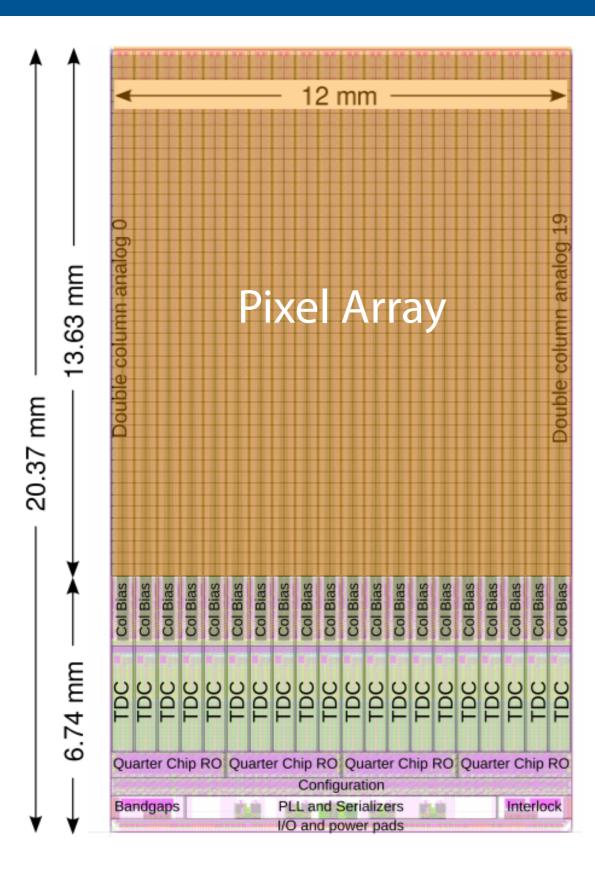

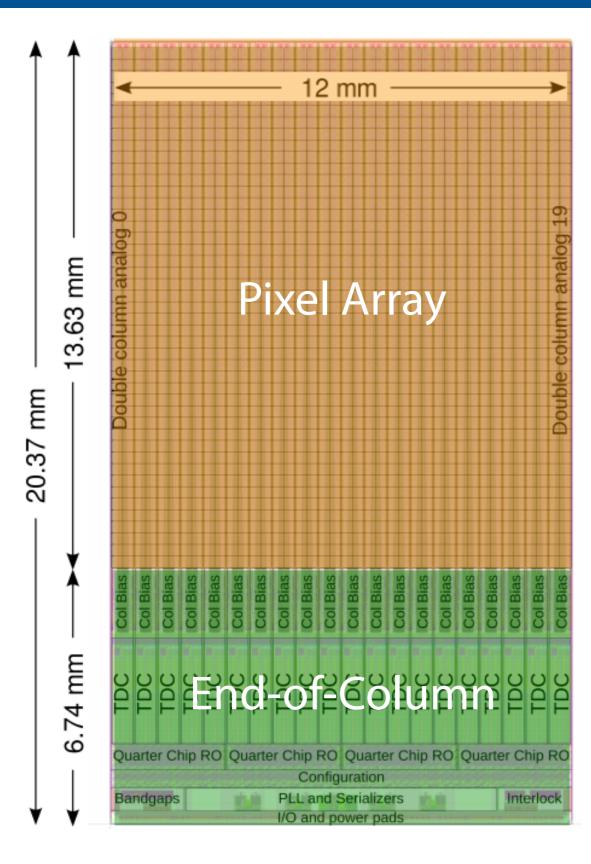

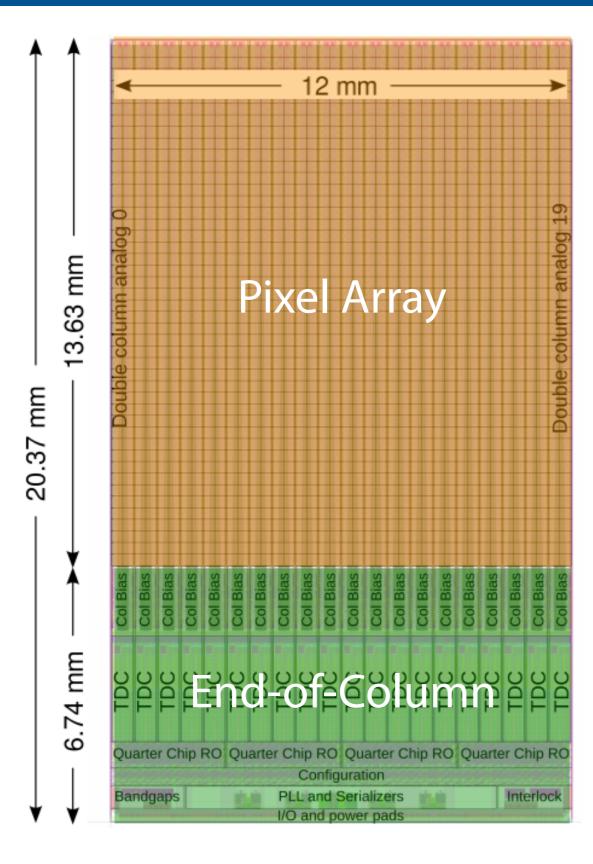

Design by Cern PH-EFE: -1800 pixels (40col × 45pix)

-each pixel (300 × 300) µm<sup>2</sup>

-separate analog-digital: no high freq clock to pixels

Design by Cern PH-EFE: -1800 pixels (40col × 45pix) -each pixel (300 × 300) µm<sup>2</sup> -separate analog-digital: no high freq clock to pixels

#### Pixels integrate:

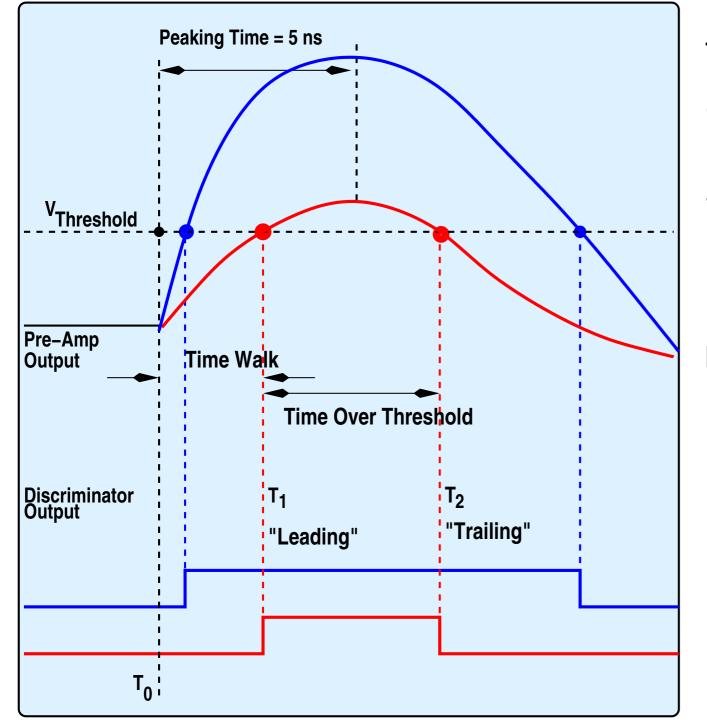

- amplifier (70mV/fC, 5ns peak. time)

discriminator

- -DAC threshold trim

- -configuration register

Design by Cern PH-EFE: -1800 pixels (40col × 45pix) -each pixel (300 × 300) µm<sup>2</sup> -separate analog-digital: no high freq clock to pixels

#### Pixels integrate:

- -amplifier (70mV/fC, 5ns peak. time) -discriminator

- -DAC threshold trim

- -configuration register

#### **End of column (EoC) integrates:**

-time-to-digital converters (TDC) -data serializers

Design by Cern PH-EFE: -1800 pixels (40col × 45pix) -each pixel (300 × 300) µm<sup>2</sup> -separate analog-digital: no high freq clock to pixels

#### Pixels integrate:

- -amplifier (70mV/fC, 5ns peak. time) -discriminator

- -DAC threshold trim

- -configuration register

#### End of column (EoC) integrates:

-time-to-digital converters (TDC) -data serializers

Power consumption: ~3.5W, mostly EoC

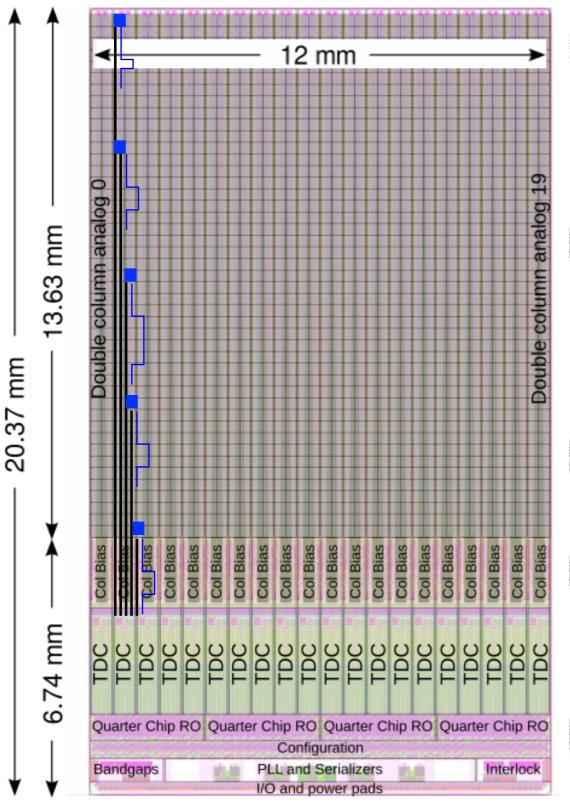

# **TDCPix End of Columns**

Signals from 5 non adjacent pixels in a column are sent to a multiplexer (HitArbiter)

▶Each HitArbiter has a TDC pair measuring leading and trailing edges → 360 TDC pair/chip

▶TDC have 100 ps bins

Self triggered operation: rate 210 MHits/s

Data sent out using four 3.2 Gb/s serializers

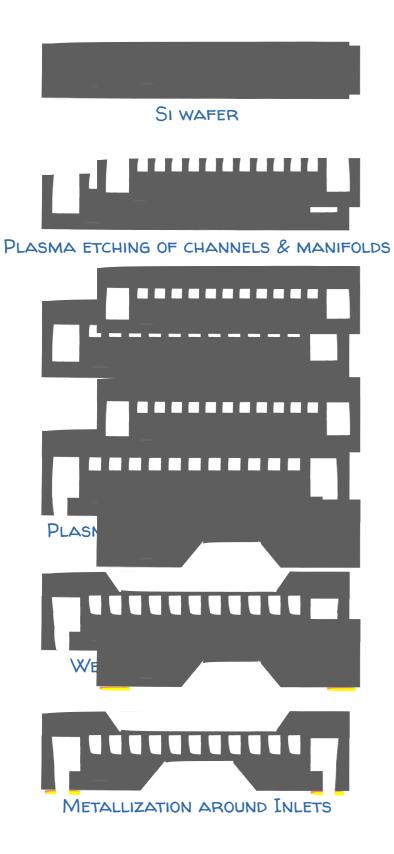

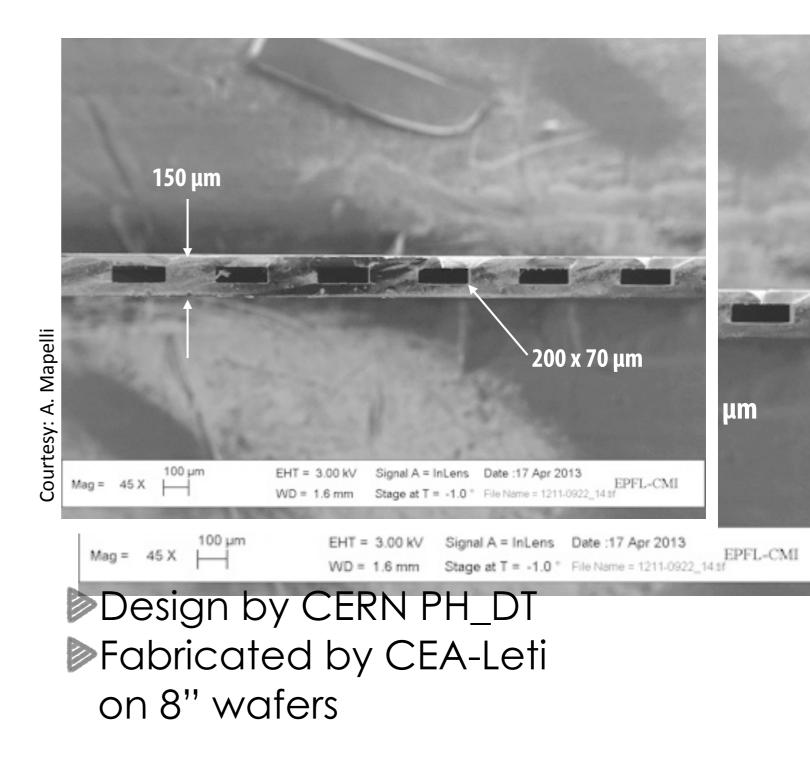

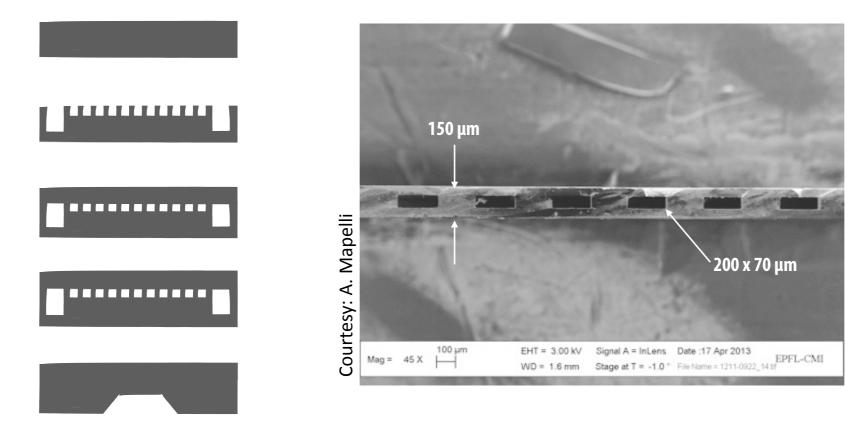

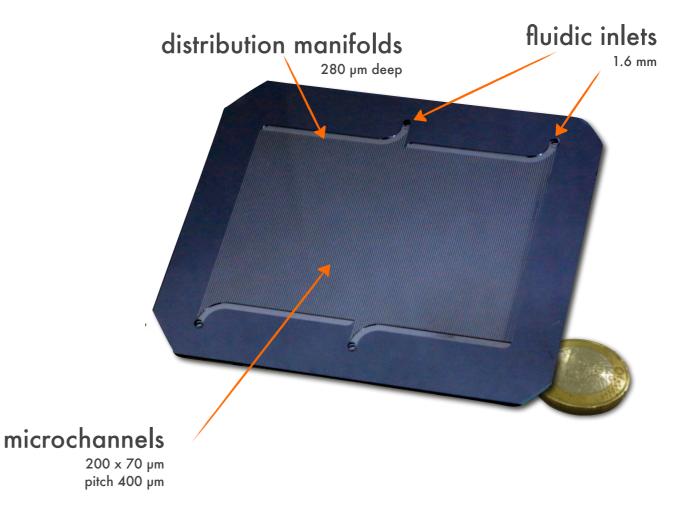

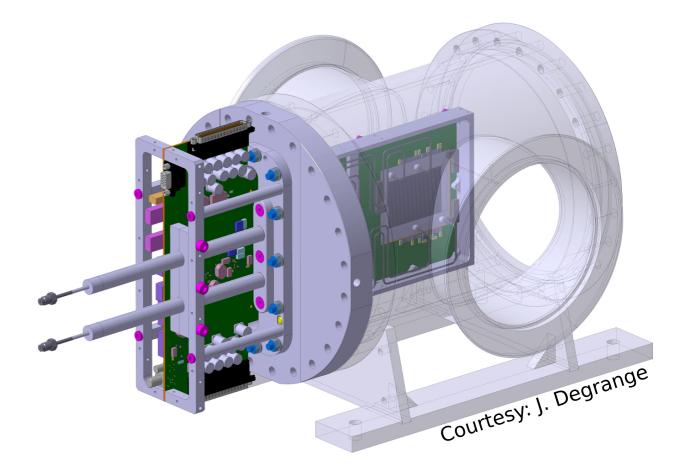

# Microchannel cooling

Physics performance requires to minimize the material budget

Detector is in vacuum

Need to dissipate ~35 W/station

Micro-channel cooling matches the constrains: ▶designed by Cern PH-DT group ▶silicon-silicon assembly, (200 × 70) µm<sup>2</sup> channels

Now material budget: 130 µm of silicon (< 0.15% X₀)</p>

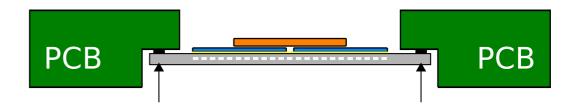

#### ▶Detector glued on 130 µm Silicon Cooling Plate

▶Detector glued on 130 µm Silicon Cooling Plate

Cooling plate is clamped onto PCB

▶Detector glued on 130 µm Silicon Cooling Plate

Cooling plate is clamped onto PCB

PCB is glued into frame and flange

Detector glued on 130 µm Silicon Cooling Plate

Cooling plate is clamped onto PCB

PCB is glued into frame and flange

Flange closes the vacuum vessel

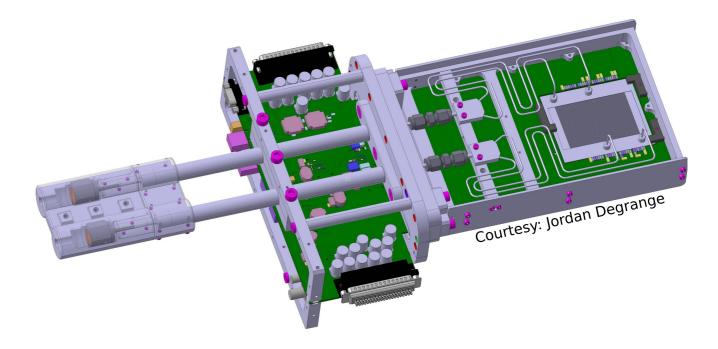

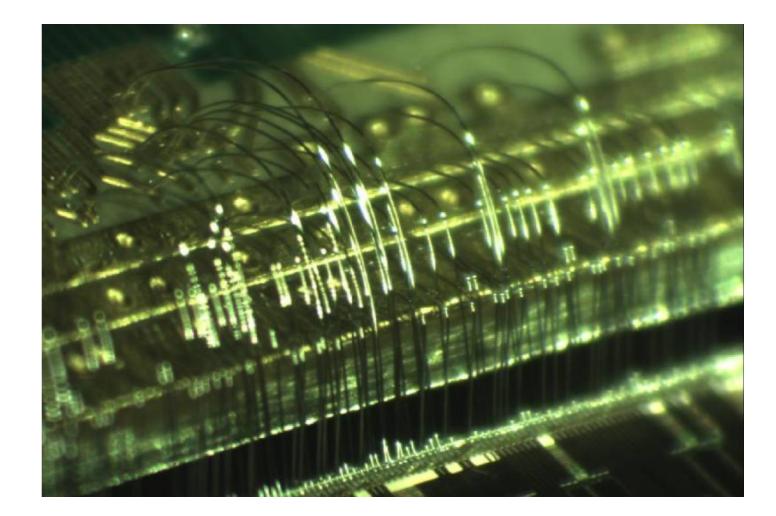

# **Electrical** integration

►TDCPix wired bonded to PCB: dense wire-bonding scheme (73 µm pitch on chip)

- PCB routes power, clock, control and signal lines to/from the off-detector electronics

- ▶Complex PCB:

- 14 layers

- 40 differential 3.2 Gb/s signals over 30 cm

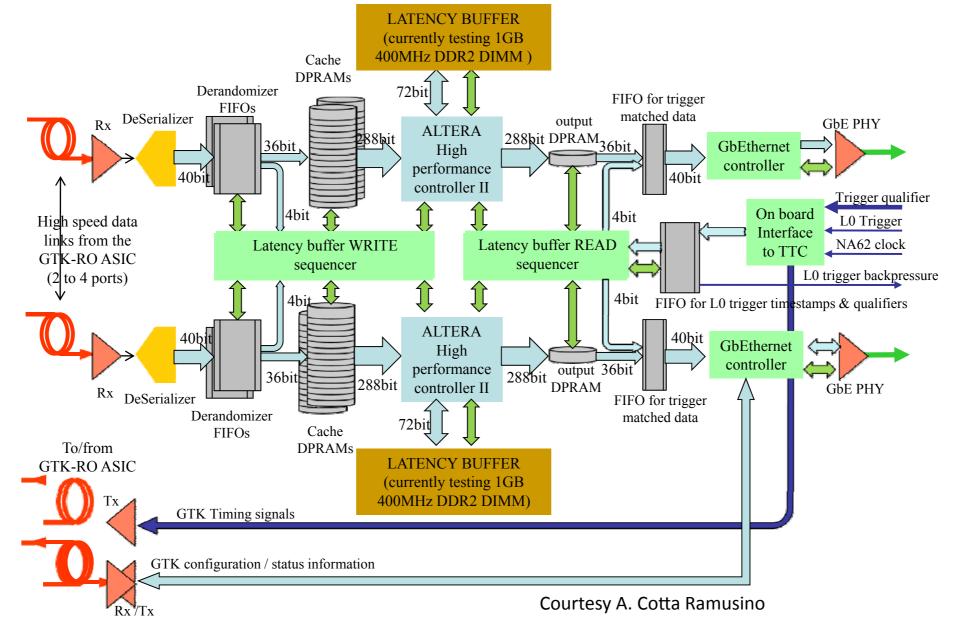

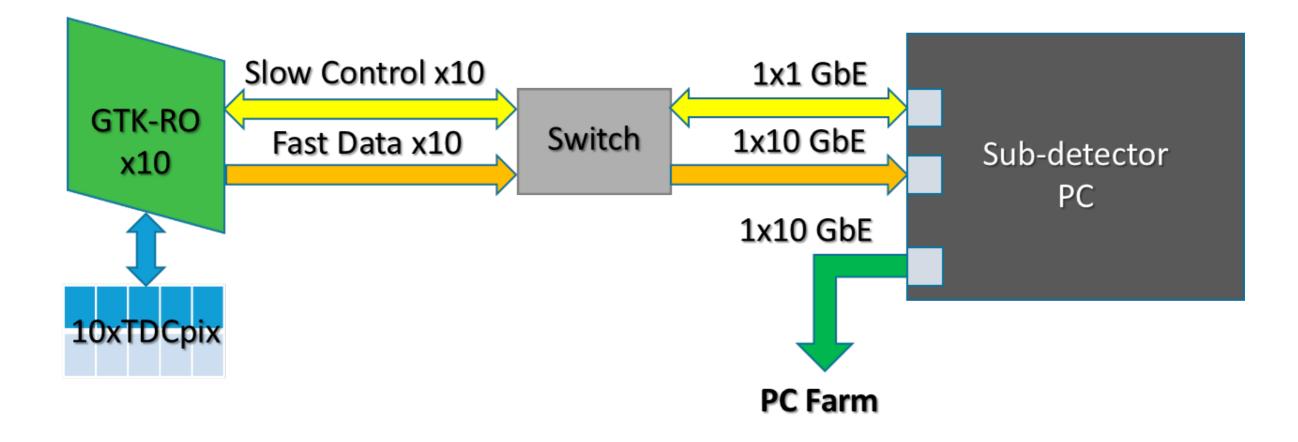

# Data acquisition- GTK-RO

TDCPix sends out every hit: trigger matching needed

GTK-RO built using FPGA (Altera Stratix GX110)

Each GTK-RO made of two decked cards: daughter card handles interface with TTC

Each TDCPix is connected to one DAQ board (GTK-RO) through 4 optical links (one per TDCPix 3.2 Gb/s serializer) + 1 configuration link. Transmission is data driven

# Data acquisition- GTK-RO

GTK-RO board must

- buffer data, waiting for level-0 trigger decision (max level-0 trigger latency is 1 ms)

- retrieve data in a 75 ns time window upon each trigger request, and send them to the subdetector PC using UDP

### Data acquisition- GTK-RO

GTK-RO board must

- buffer data, waiting for level-0 trigger decision (max level-0 trigger latency is 1 ms)

- retrieve data in a 75 ns time window upon each trigger request, and send them to the subdetector PC using UDP

### Data acquisition- Detector PC

Assemble data from several GTK-ROs and send it to the online farm

Plain linux distribution as O.S. with "zero copy" module of PF\_RING to reduce memory to memory copy.

Multiple threads to handle the amount of data (worst case ~82 MB/s from each chip+protocol overhead)

Changes in 2016

Spikes in instantaneous beam intensity  $\rightarrow$  use 2 PCs/station

Possibility to become L1-detector: GTK data not used for first sw trigger → readout GTK only in response to L1 triggers

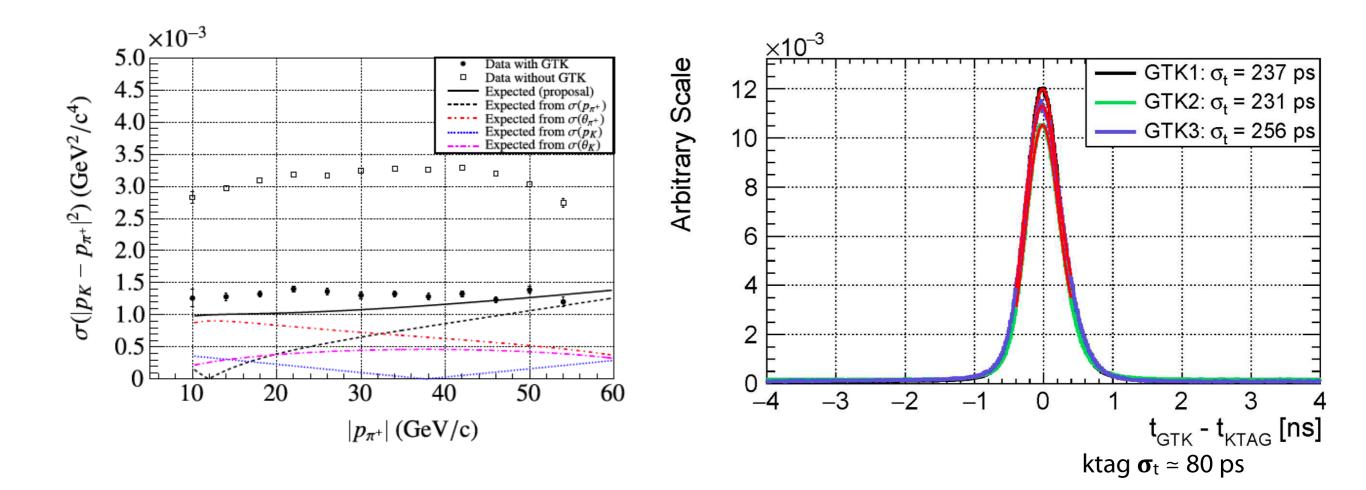

### Results

All stations + infrastructure installed and commissioned in 2015

GTK cooled at 0 °C (2 g/s of C<sub>6</sub>F<sub>14</sub> at 3 bar), thresholds set to 0.7 fC, bias voltage ~300V

$\blacktriangleright$  time resolution  $\simeq 215 \text{ ps} @ 300 \text{V}$

# Thank you for your attention

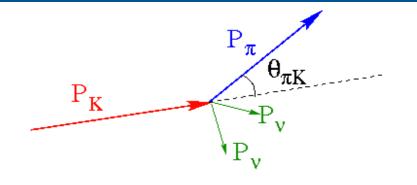

### NA62 signal and background

Signal:

$$m_{miss}^2 = (P_K - P_\pi)^2$$

Background:

- a) K<sup>+</sup> decay modes

- b) accidental single track matched with K-like one

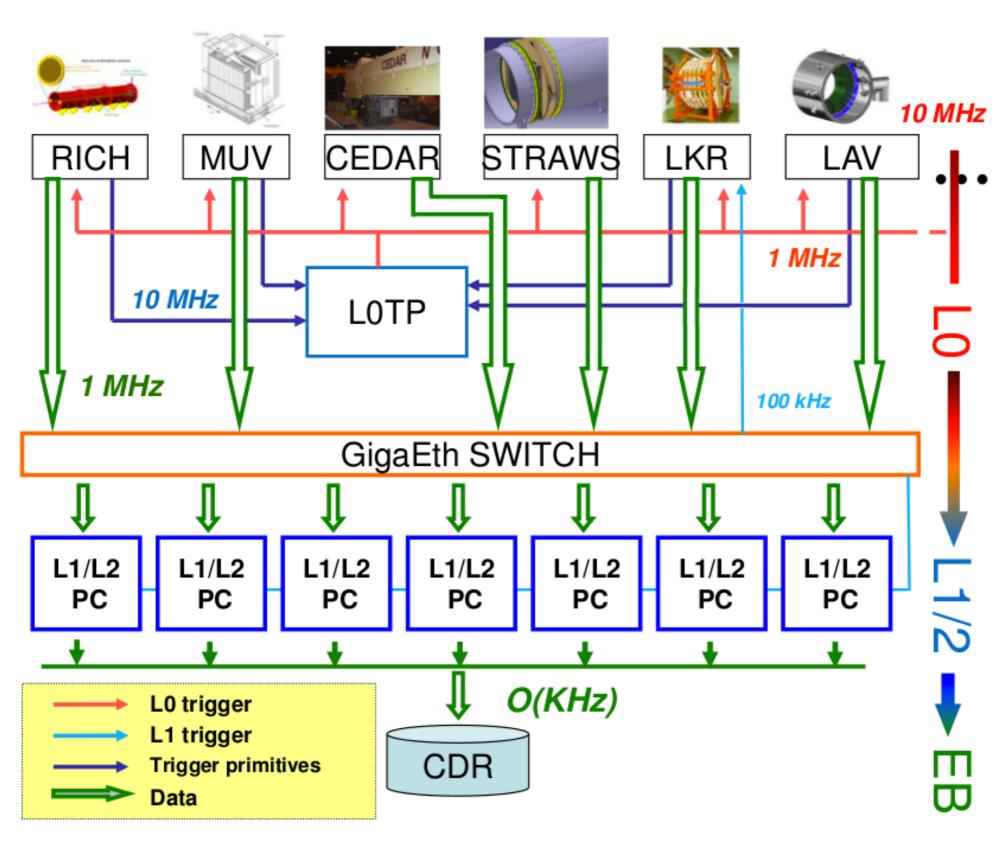

# Trigger and Data Acquisition (TDAQ)

LO: hw synchronous level. 10 MHz to 1 MHz

Max latency 1 ms

L1: sw level. "Single detector". 1 MHz to 100 kHz. Max latency O(1s)

L2: sw level. "Complete information". 100 kHz to 10 kHz. Max latency O(30s)

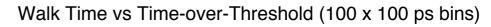

### Time-over-threshold - Time-walk correction

Time walk correction takes advantage of the relation between time walk and time-over-threshold.

Essential to meet the hit time resolution requirement

# Microfabrication of the cooling plates