## Multiple Fast Controller Synchronization for ITER Control System Model

Author: Martynas Prokopas (Fusion-DC / IST / ITER)

Co-authors: Bertrand Bauvir (ITER Organization), Anders Wallander (ITER Organization), Jorge Sousa (IST Institute)

Promoters: Instituto Superior Técnico (IST), ITER Organization, Università degli Studi di Padova

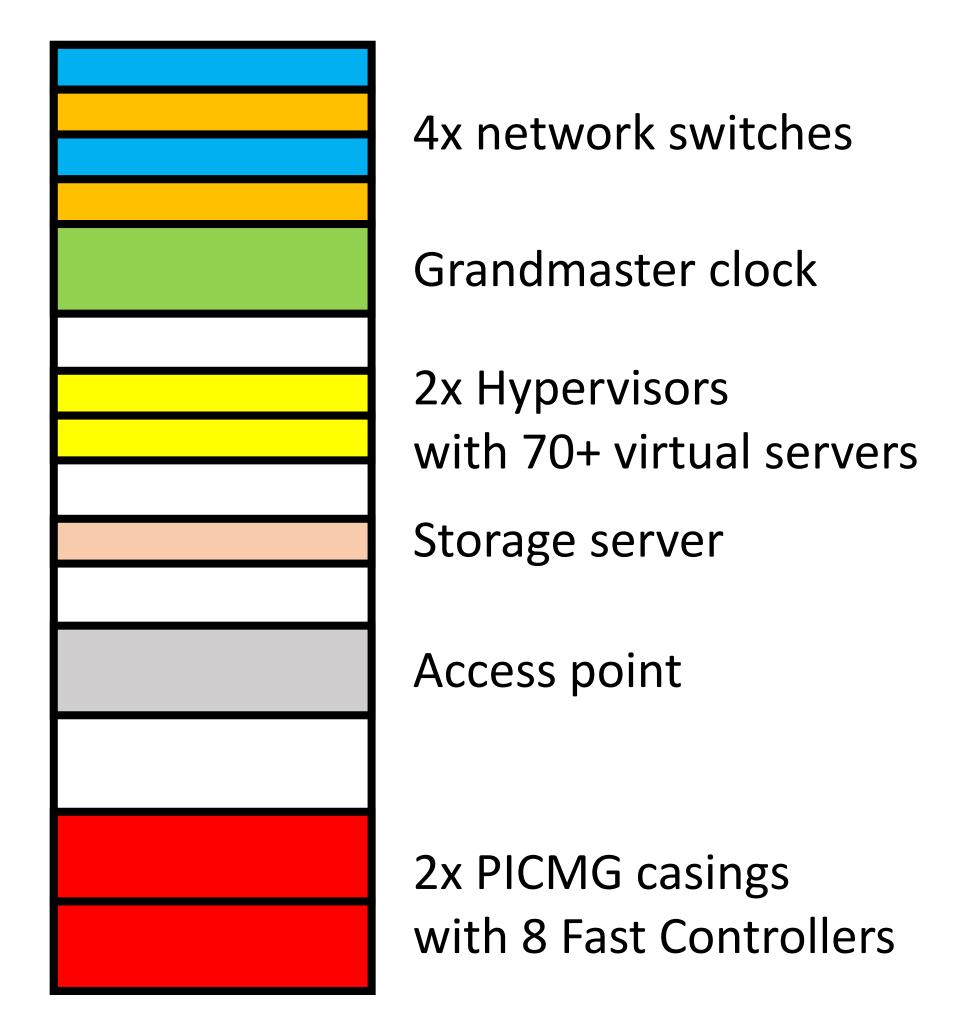

## Control Model infrastructure

- Full-scale simulation of CODAC (ITER control system) without any physical I/O

- Standard server configuration and CODAC software

- Following all CODAC naming conventions

- Servers connected over physical networks and their dedicated switches to simulate real-world performance

- Fully automated deployment procedure without any manual configuration of individual servers

## Real-Time infrastructure includes:

- 8x Fast Controllers (2x Xeon E3, 3x Xeon E5, 3x Core i7)

- 8x T420-CR Chelsio 10GbE network adapters

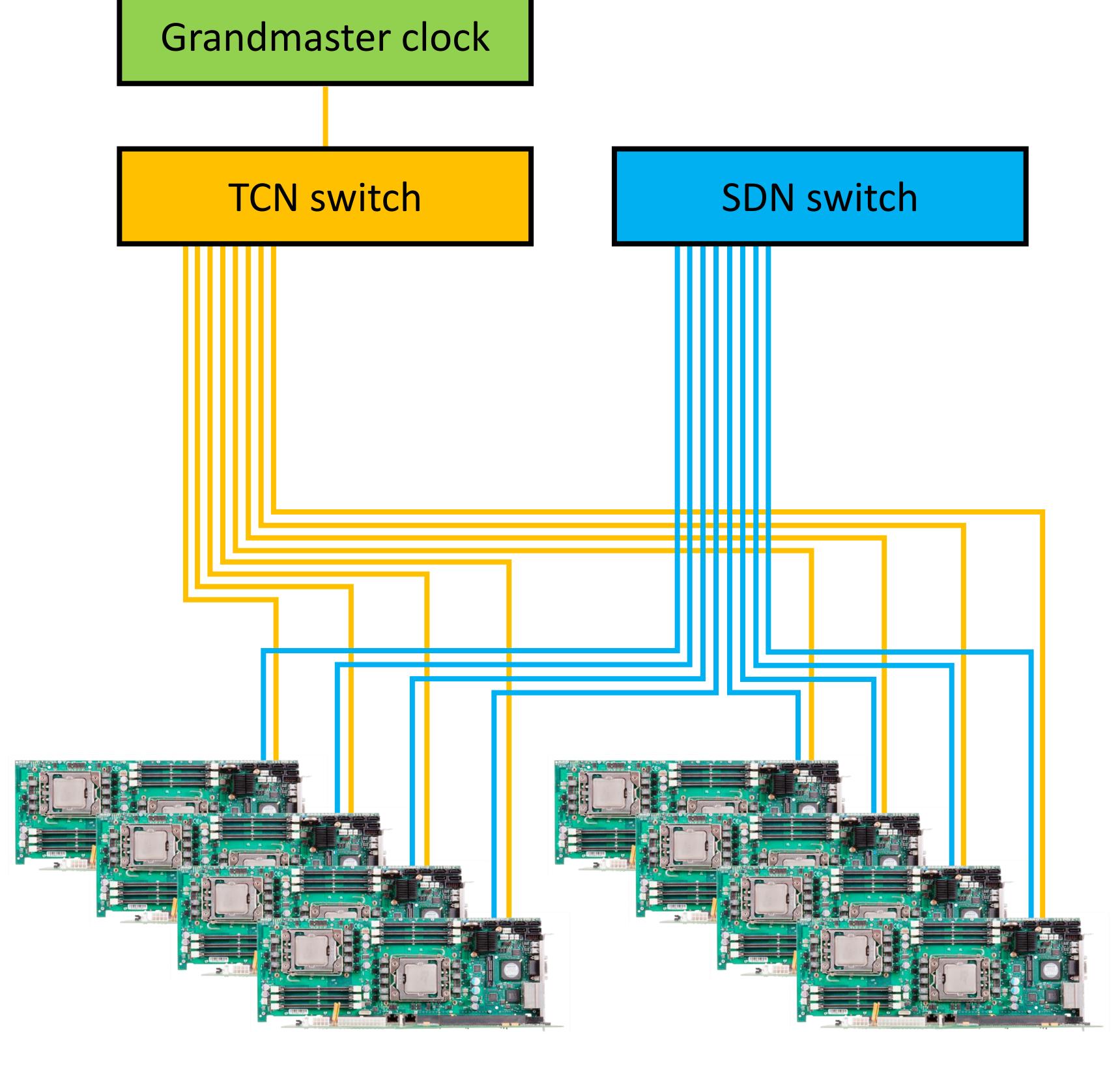

- Grandmaster clock and a dedicated switch using IEEE 1588-2008 standard over UDP/IP (synchronizing via PTPv2 protocol), which represent ITER Time Communication Network (TCN)

- Multicast capable cut-through high performance switch over UDP/IP for simulating ITER Synchronous Databus Network (SDN)

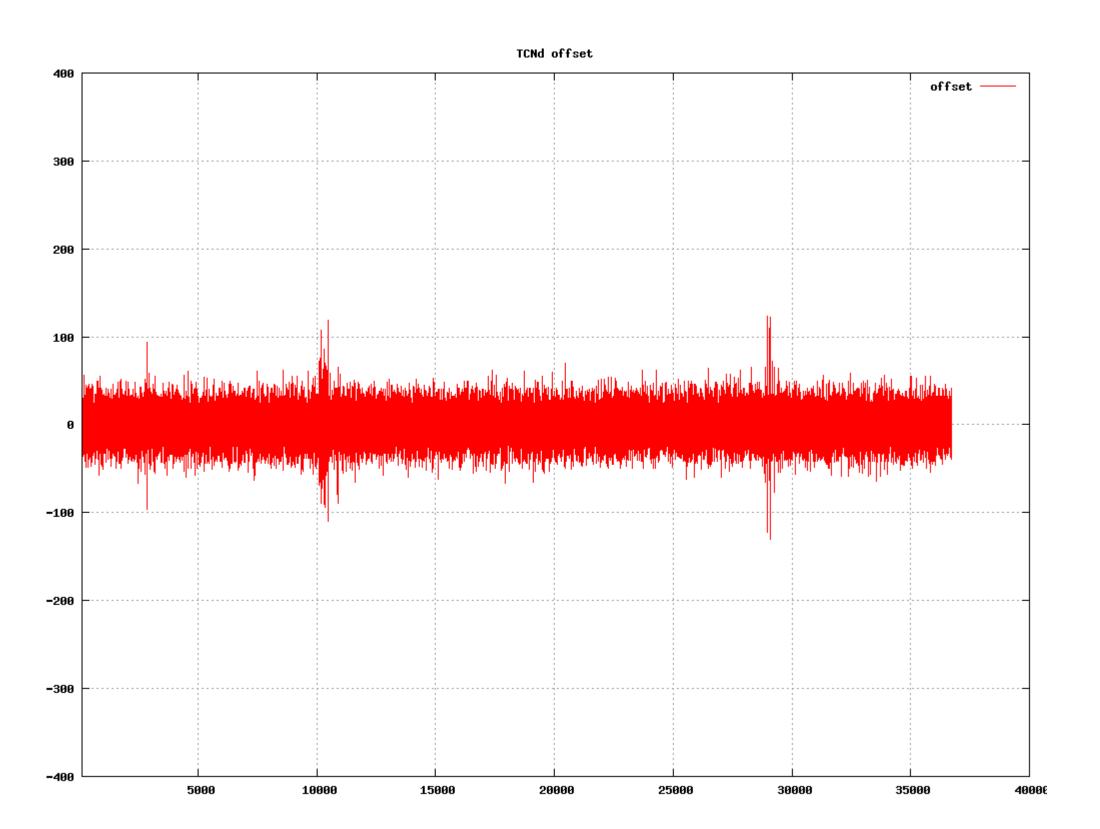

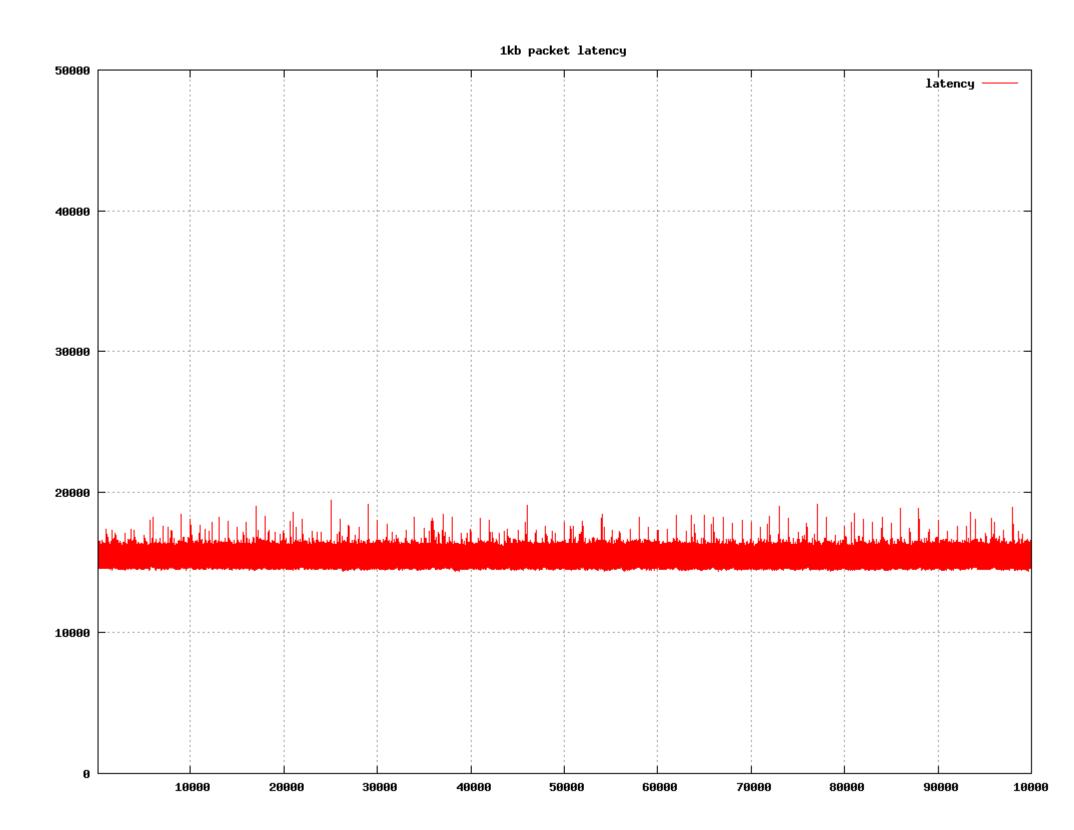

## Real-Time configuration

System clock synchronization as low as 20 ns rms\*

1KB packet transfer latency as low as 15 μs\*

\*optimization still in progress

- 2x Intel Xeon E3-1275

- 3x Intel Xeon E5-2428L

- 3x Intel Core i7-4790S

All paired with a 10 GbE T420-CR Chelsio adapter