# Single-Photon Avalanche Diode detector for Raman spectroscopy with time-gated fluorescence suppression

Herman Larsen (corresponding author: herman.larsen@stfc.ac.uk), Luca Ciaffoni, Nicola Guerrini, Pavel Matousek, Iain Sedgwick, Nick Waltham UKRI-STFC Rutherford Appleton Laboratory Didcot, Oxfordshire, OX11 0QX

#### I. Introduction

Single-photon avalanche diode (SPAD) detectors are revolutionising modern imaging and spectroscopy thanks to detection capabilities at the level of individual photons and ultrafast response times. Very recently, time-gated cameras based on SPAD technology have been proposed for improving the performance and applicability of Raman spectrometers through addressing the suppression of fluorescence interference in the most commonly used, near infrared spectral region – one of the greatest, largely unmet, challenges in modern Raman spectroscopy. However, existing solutions are at present restricted to a small subset of samples and regimes of operations due to low near-infrared (>800 nm) sensitivity, low frame rates and small (often 1D) array formats.

## II. Raman Spectroscopy—The Challenge

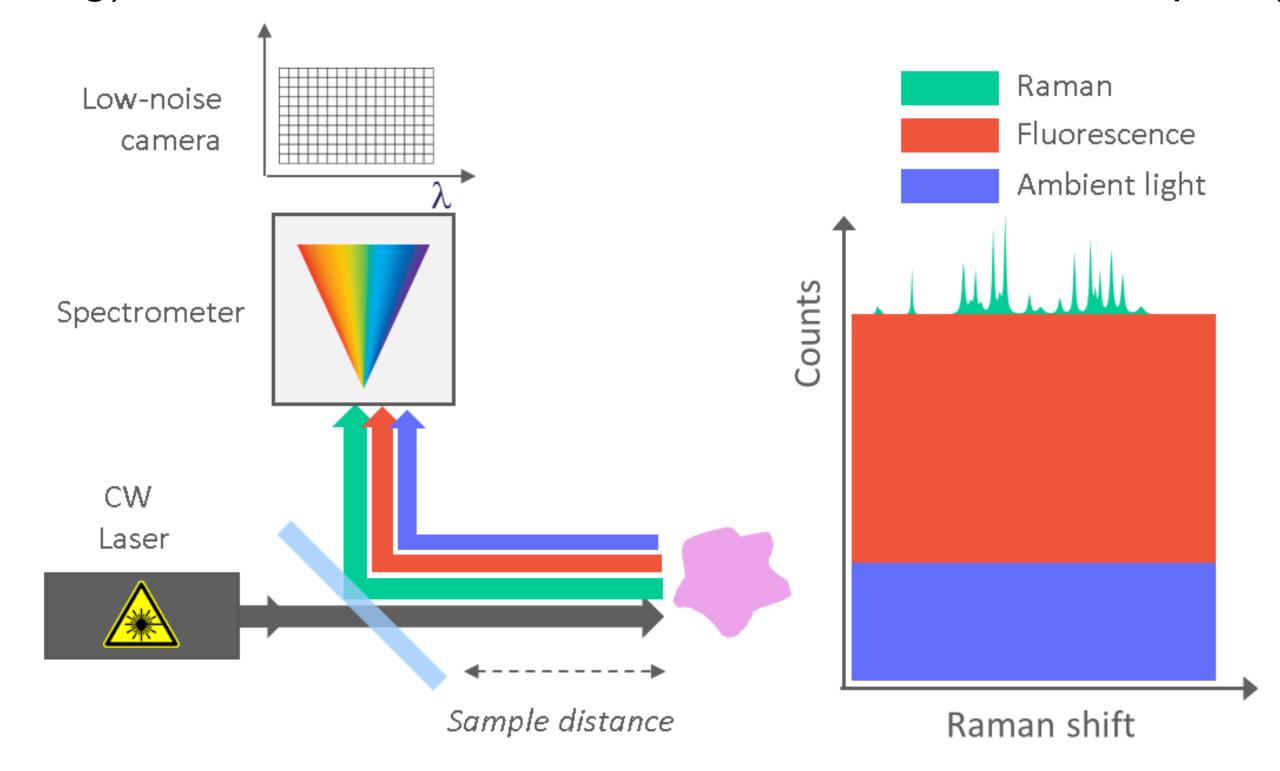

Raman spectroscopy uses a monochromatic light source to illuminate a sample of interest. Inelastic scattering of the incoming photons leads to a wavelength shift which can be detected and used to characterise the sample. However, molecular Raman signatures are typically very weak, and their accurate detection is made notoriously difficult by the presence of often overwhelmingly strong fluorescence (from the sample/laser interaction) and/or ambient light background signals (if the procedure is carried out without light shielding), illustrated below. Here we can see a sample (pink)

illuminated by a laser (black). The desirable Raman signal (green) is hugely dominated by the fluorescence of the sample (red) and the ambient background (blue). The effect on the total count rate is shown on the right. It can be seen that the background signals dominate the Raman signal, and are effectively noise.

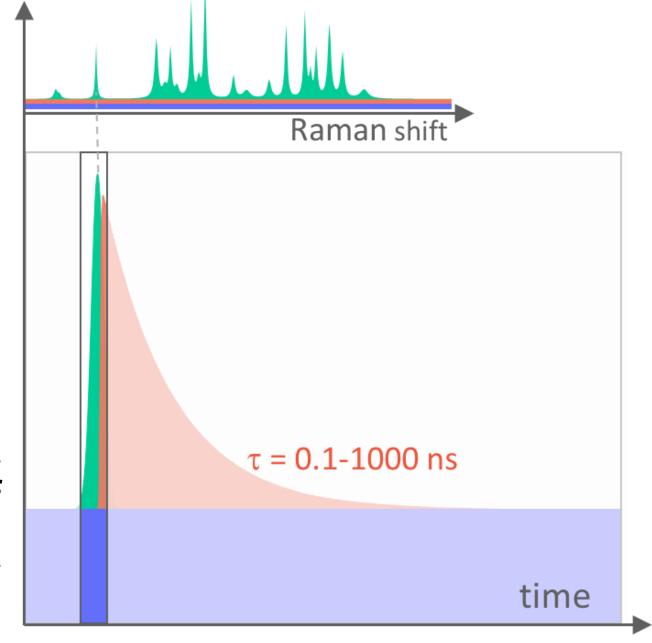

There is a limit to the degree to which filtering and optical design can

limit this effect. However, one possible way to separate Raman light from the fluorescence signal is in the time-domain. The Raman signal arrives very rapidly after the illumination, whereas the fluorescence is a slow decay. Therefore, if the receiving device can be time-gated, the Raman signal can be extracted with limited fluorescence background, illustrated here. A short window also has the advantage of limiting the number ambient light photons which are collected.

However, the challenge is not only to apply this time gate. Fluorescence can be further reduced be operating in the Near-Infrared (NIR) band, and for a practical detector system there are further considerations. A large imaging array will improve the results—larger in the X-direction lead to higher spectral resolution, larger in the Y-directions leads to a larger light collecting area and

higher signal. Operating at a high frame rate is desirable for practical reasons. It reduces the time needed for the measurement, allowing higher throughput and less risk of instability of the sample or background conditions during the experiment.

#### III. IRIS

With the goal of addressing these limitations, we present IRIS, a SPAD based sensor for Raman Spectrometry.

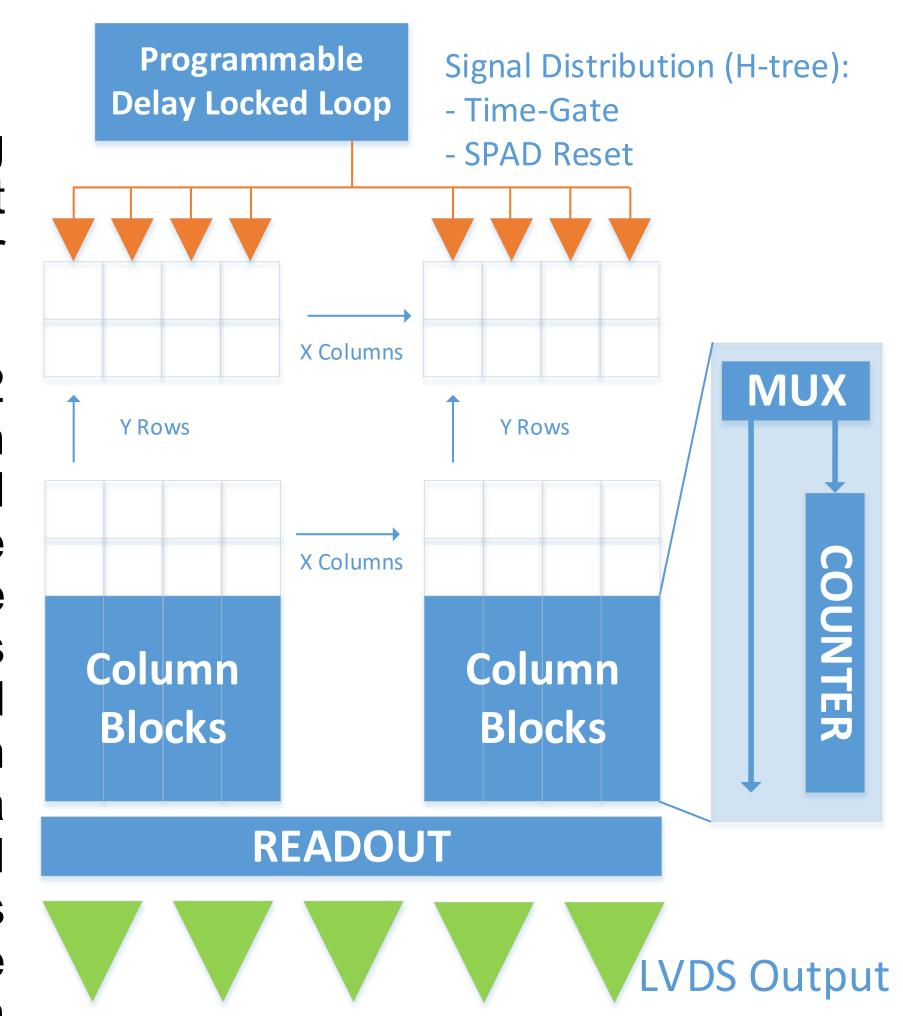

IRIS consists of a 100x92 array of SPAD pixels which are gated by a distributed pulse to make them sensitive only during the "Raman" time The period. pulse is generated by an on-board DLL, which allows its position to be locked relative to a laser trigger, and adjusted within the period of this architecture The trigger. sums hits in each column

over 256 frames to build a histogram of counts corresponding to hits within each spectral band. These sums are then transmitted off-chip.

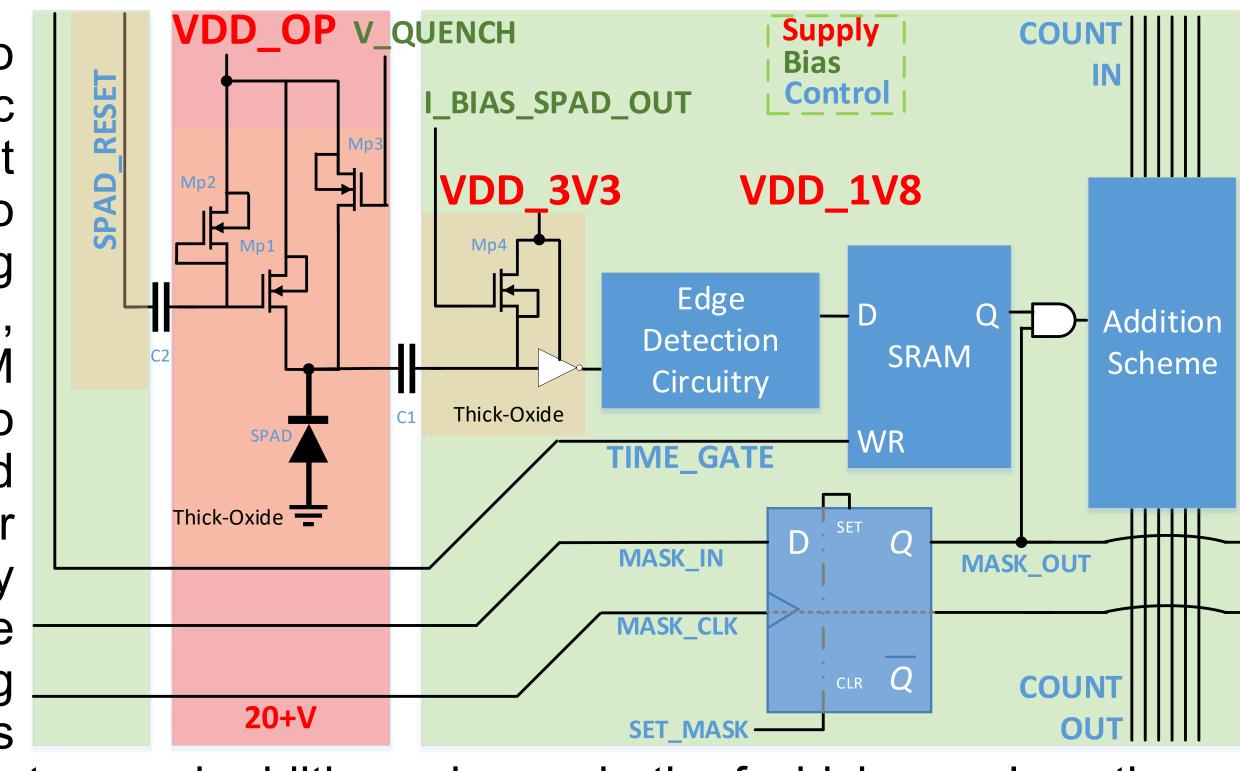

The pixel itself has a pitch of 30 µm. It consists of the SPAD and its related quenching and active reset circuitry. This circuitry continuously passively quenches the SPAD and actively resets it within 3-4 ns at the start of each frame if it was previously hit. The high voltage SPAD region is capacitively coupled to the 3.3/1.8 V logic, and a logic falling edge is produced when hit.

The pixel also contains logic limit hit recording the incoming gate period, SRAM memory store hits, and mask for blocking noisy The pixels. two remaining pixel regions

form the clock tree and addition scheme, both of which run along the full column. The clock-tree distributes the 200 ps time-gate at less than 20 ps spread between arrival at first and last pixel. This ensures the time-gate from the DLL is distributed with minimal skew across the full array — certainly less than the 180 ps jitter of the SPAD itself. This tree is shared between pairs of columns to reduce power consumption and pixel pitch.

The addition scheme counts pixel hits within one column, and is designed to function at up to 40 MHz when scaled to 256 pixels per column. To meet this speed requirement, a sequential pipeline scheme was designed, allowing some parallel computation whilst reducing the overall combinational delay.

### IV. Status and Future Work

The chip has been submitted, and test results will be presented in a future publication. Some early application areas have been identified, but groups interested in using the device for their own applications are actively sought and should contact the authors.