# ATLAS LI Calo

**Status Report**

## **Current System: Developments**

- New PreProcessor MCM

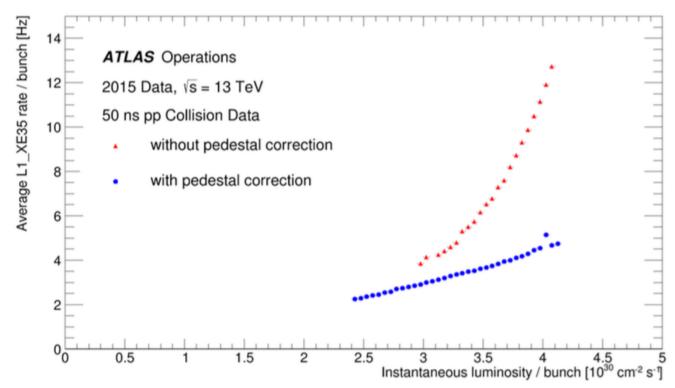

- More pileup-robust filters

- BC-dependent baseline correction

- Large input from Andrew Daniels

## **Current System: Developments**

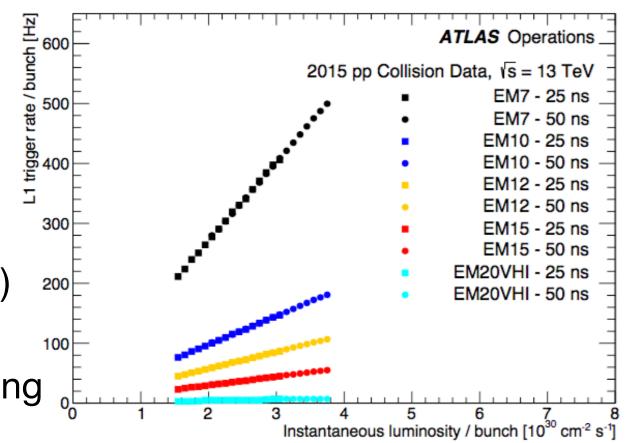

## • EM/Tau Trigger

### • Changes to dataflow to support L1Topo

- Changes to isolation algorithms (LUT-based, ETdependent)

- Changes to data supplied to CTP

- B'ham Contribute

- <sup>o</sup> Firmware, hardware

- Software (on/off-line)

- <sup>o</sup> Operations

- Calibration, Monitoring

**ATLAS L1Calo Status**

## Upgrade: Phase I

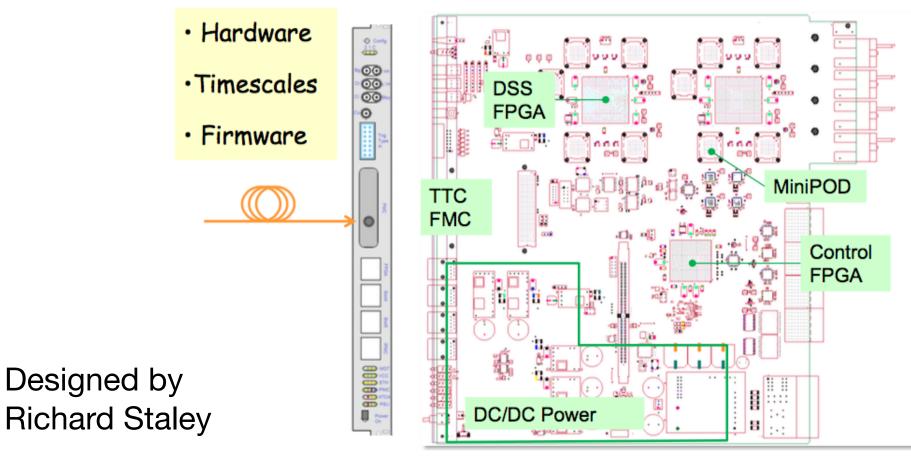

### • Fex Test Module

#### Multi-purpose high-speed data source for testing of Phase I processors

## FTM Hardware Status

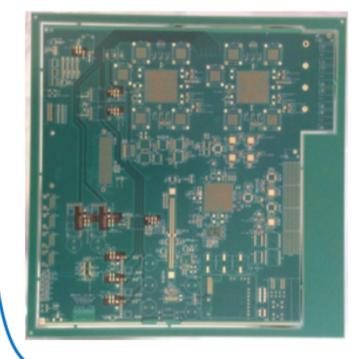

#### 4 bare PCBs ordered (Isola I-Tera material, 22 layer)

→ 1 retained by fabricator → 3 delivered to Assembly company ↓ 1 dispatched to RAL (9<sup>th</sup> Sept) Impedance OK +/- 10%

#### Module Assembly

2 PCBs being assembled.

Est. delivery 2<sup>nd</sup> Oct to RAL

Power + JTAG, then onto B'ham

Replacement bare PCB expected 19<sup>th</sup> October (+2 to 3 weeks Assy.)

R.Stalev. L1 Calo Trigger Joint Meeting - KIP / Heidelberg - 01/10/2015

3

## Upgrade: Phase-II

## **Upgrade:** Phase-II

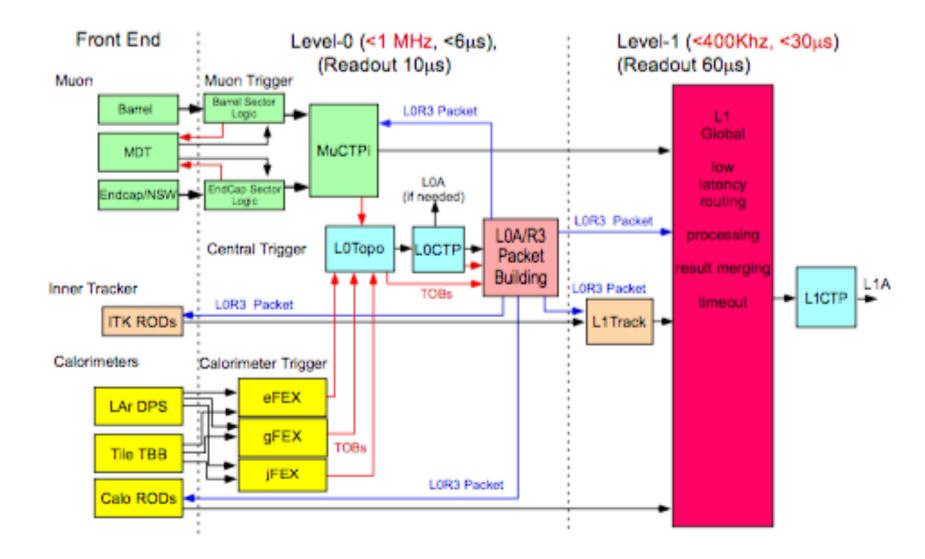

#### Level-1 Global chapter in IDR

| 7 | Level-1 Global Trigger |        |                                              |    |

|---|------------------------|--------|----------------------------------------------|----|

|   | 7.1                    | Introd | uction                                       | 40 |

|   | 7.2                    | Algori | thms                                         | 40 |

|   |                        | 7.2.1  | Jets and $E_{\rm T}^{\rm miss}$              | 40 |

|   |                        | 7.2.2  | $e, \gamma$ and $\tau$                       | 40 |

|   |                        | 7.2.3  | Muons                                        | 41 |

|   |                        | 7.2.4  | Multi-object triggers                        | 41 |

|   | 7.3                    | Netwo  | rk topology within L1Global                  | 41 |

|   |                        | 7.3.1  | Event data volume                            | 41 |

|   |                        | 7.3.2  | Dead time considerations                     | 42 |

|   |                        | 7.3.3  | Number of Event Processors                   | 42 |

|   |                        | 7.3.4  | Mapping between sources and Event Processors | 42 |

|   |                        | 7.3.5  | Aggregator layer with queuing                | 43 |

|   |                        | 7.3.6  | Data mapping                                 | 45 |

|   | 7.4                    | Physic | al realisation                               | 45 |

|   |                        | 7.4.1  | Event Processors                             | 45 |

|   |                        | 7.4.2  | Aggregator layer                             | 45 |

|   |                        | 7.4.3  | Global Trigger interfaces                    | 45 |

|   |                        | 7.4.4  | Overall latency                              | 46 |

|   | 7.5                    | Work 1 | plans for TDR                                | 46 |