### **Device structures: monolithic**

Eva Vilella

University of Liverpool

vilella@hep.ph.liv.ac.uk

#### Eva Vilella – Who I am...

#### **Device structures: monolithic**

- Monolithic refers to detectors that integrate the <u>sensing element</u> and <u>readout chip</u> in a single layer of silicon:

- CMOS

- HV-CMOS

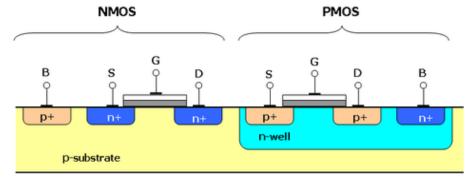

- Both CMOS and HV-CMOS are <u>the</u> industry standard fabrication processes for MOSFET transistors used in integrated circuits (IC) chips:

- CMOS (Low Voltage)

- Image sensors

- Microprocessors

- Microcontrollers

- Memories

- Transceivers for communication

- HV-CMOS = CMOS + High Voltage substrate biasing &

additional wells to isolate the electronics from the substrate

- Display and motor drivers

Wikipedia

I. Kremastiotis, arXiv:1706.04470v2, 2017

#### **Device structures: monolithic**

- Can we use CMOS and HV-CMOS processes to fabricate detectors for physics experiments?

- Absolutely yes!!!

I. Peric, <u>10.1109/JSSC.2021.3061760</u>, 2021

# Who are you?

https://www.smartsurvey.co.uk/s/12T2Q7/

| Eva's Instrumentation Course                                  |

|---------------------------------------------------------------|

|                                                               |

|                                                               |

| 1. What is your PhD thesis about?                             |

| CMOS or HV-CMOS R&D                                           |

| Other detector type R&D                                       |

| Physics related things (such as simulations or data analysis) |

| Other (including I don't know yet)                            |

|                                                               |

|                                                               |

**Finish Survey**

### **Particle tracking**

Follow the tracks of an animal and identify it from its footprint

Measure particle trajectories from hits they leave in silicon detectors

Connecting the dots: The **tracks** provide crucial information on a particle's direction, charge and energy.

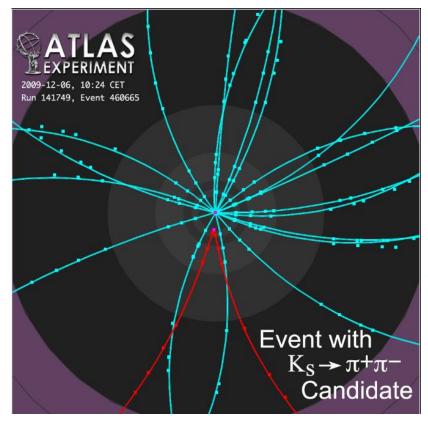

### The technological challenge

Billions of collisions per second produce 100's of billions of particles.

Above picture shows one 25 ns frame with 1000s of particles.

<u>Detectors</u>: Layers of thin silicon sensors measure accurate **hit points** along the particles' trajectories.

- Physics experiments require <u>ever more precise</u> and <u>fast detectors</u> to make high precision measurements in high intensity environments.

- Radiation tolerance is critical as detectors have to survive many years of operation.

# Silicon tracking detectors – Specifications

| Pixel size          | Small               | ~ μm x μm                                                 |   |

|---------------------|---------------------|-----------------------------------------------------------|---|

| Time resolution     | Excellent           | < 100 ps                                                  |   |

| Radiation tolerance | High                | > 10 <sup>17</sup> 1 MeV n <sub>eq</sub> /cm <sup>2</sup> |   |

| Material budget     | Minimal             | < 50 μm                                                   |   |

| Power consumption   | Minimal             | ~10-100 mW/cm <sup>2</sup>                                |   |

| Reticle size        | Large               | > 2 cm x 2 cm                                             | 7 |

| Noise               | Minimal             |                                                           |   |

| Assembly process    | As easy as possible |                                                           |   |

| Yield               | High                |                                                           |   |

| Price               | Cheap               |                                                           |   |

|                     |                     | O.W.                                                      |   |

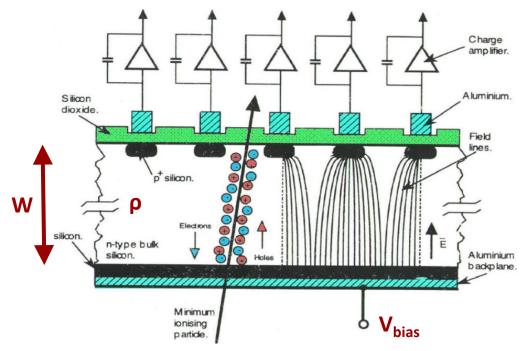

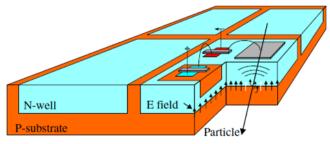

### **Sensor – Detection principle**

- Silicon p-n diode in reverse bias

- A traversing particle creates e<sup>-</sup>/h<sup>+</sup> pairs by ionization

- The electric field separates the  $e^-/h^+$  pairs, which move to the detector electrodes where they generate signal

- Basic requirements:

- Large bias voltage (V<sub>bias</sub>)

- Larger W → larger signal

- Faster charge collection

- Better radiation tolerance

- High resistivity silicon bulk (ρ)

- **Backside biasing**

- More uniform electric field lines

- Improved charge collection efficiency

- The signal is amplified, discriminated and digitized by the readout electronics

$\rightarrow$  W =  $\sqrt{\rho \cdot V_{bias}}$

On average 80 electronhole-pairs/µm of depleted region for a MIP

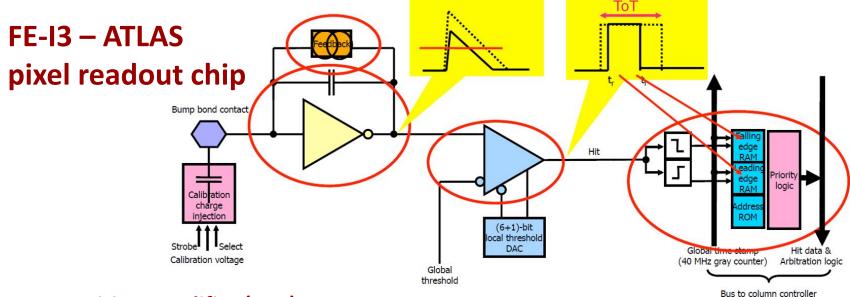

### **Readout electronics – The integrated circuit**

- Charge Sensitive Amplifier (CSA)

- Signal charge integration

- Pulse shaping (feedback capacitor with constant current)

- Comparator with DAC for local threshold voltage compensation

- Pulse digitization

- Length of digital pulse determined by time at which the rising and falling edges cross the comparator threshold voltage (Time over Threshold or ToT)

- RAM and ROM memories to store time-stamps and pixel address

- In deep sub-micron technologies for high density of integration

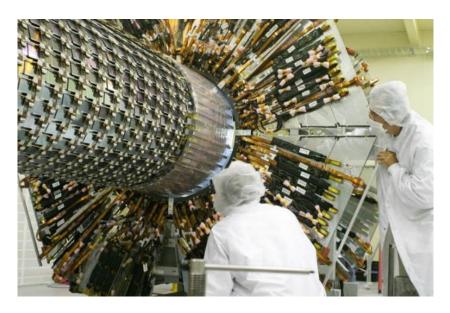

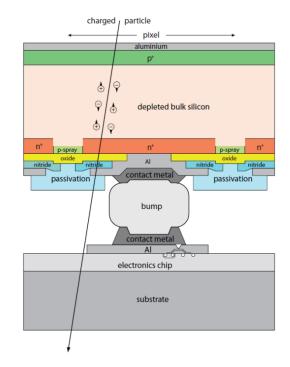

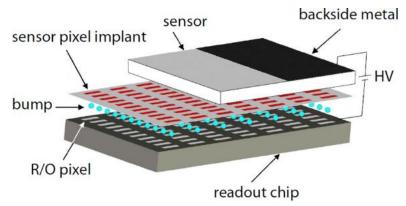

### **Hybrid pixel detectors**

- Sensor and readout electronics on separate wafers

- Best technology for the sensor and the readout electronics

- Very fast charge collection by drift (1 ns)

- Fully depleted bulk (large signal)

- Radiation tolerant (10<sup>16</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>)

- Capability to cope with high data rates

- 1-to-1 connection between sensor and readout chip via tiny conductive bumps using bumping and flipchip technology

- Limited pixel size (55 μm x 55 μm)

- Substantial material thickness (300 μm)

- Limited fabrication rate (bump-bonding and flip chipping is complex)

- Expensive (> £1M/m²) custom wafers and processing

- State-of-the-art for high rate experiments

M. Garcia-Sciveres, arXiv:1705.10150v3, 2018

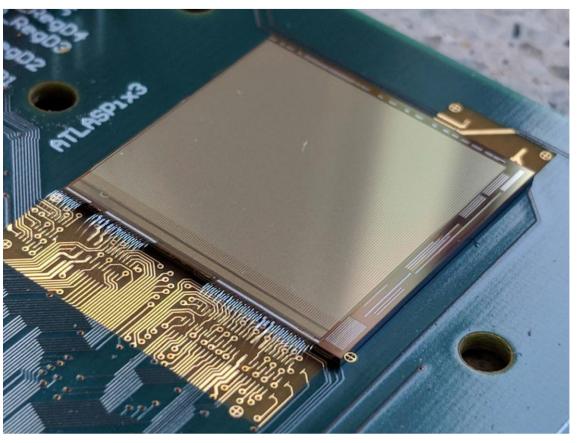

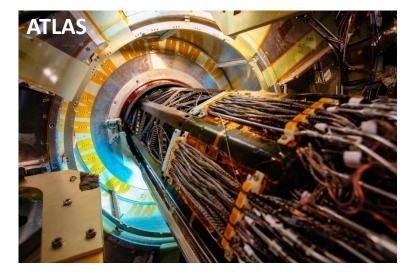

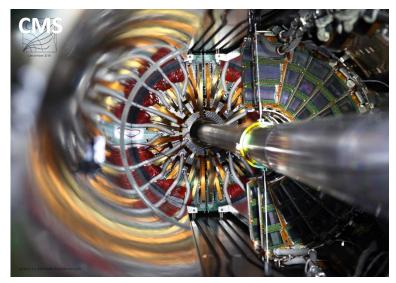

# Hybrid pixel detectors in particle physics

- ATLAS, CMS and ALICE use hybrid pixel detectors near the interaction point

- Complemented by hybrid strip detectors at larger radii

- Largest detector systems ever built in HEP (several m<sup>2</sup>)

CMOS/HV-CMOS technology applications

# **CMOS/HV-CMOS technology**

- Why is it so popular?

- Reliable (industry-standard)

- Low-power consumption

- Low-cost

- Scalable (millions of transistors are integrated into a single chip)

- Starting material is silicon (sand)

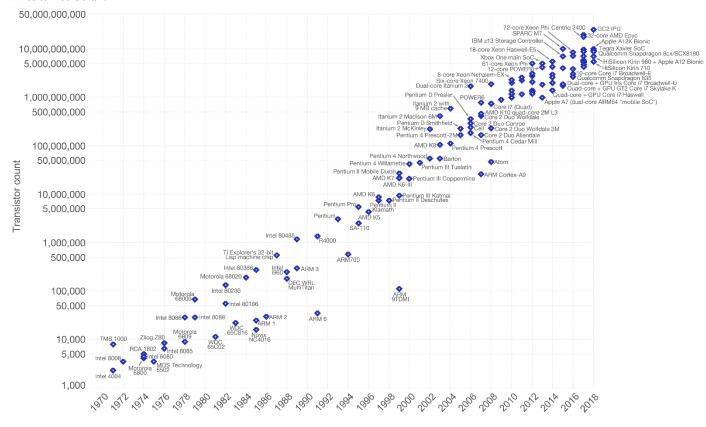

Moore's law (1965) → The number of transistors in a dense integrated circuit (IC) doubles about every two years

#### Moore's Law – The number of transistors on integrated circuit chips (1971-2018)

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important as other aspects of technological progress – such as processing speed or the price of electronic products – are linked to Moore's law.

Data source: Wikipedia (https://en.wikipedia.org/wiki/Transistor\_count)

The data visualization is available at OurWorldinData.org. There you find more visualizations and research on this topic.

Licensed under CC-BY-SA by the author Max Roser.

### **CMOS/HV-CMOS** commercial vendors

ON Semiconductor®

### **CMOS/HV-CMOS** commercial vendors

| Foundry → Parameter ↓ | LFOUNDRY<br>A SMIC COMPANY | TOWERGLE The Global Specialty Foundry Leader | TSI<br>SEMICONDUCTORS |

|-----------------------|----------------------------|----------------------------------------------|-----------------------|

| Feature node          | 150 nm                     | 180 nm                                       | 180 nm                |

| HV                    | Yes                        | No                                           | Yes                   |

| HR                    | Yes                        | Yes                                          | Yes                   |

| Quadruple well        | Yes                        | Yes                                          | Yes                   |

| Metal layers          | 6                          | 6                                            | 6                     |

| Backside processing   | Yes                        | Yes                                          | No                    |

| Stitching             | Yes                        | Yes                                          | Yes                   |

# **Monolithic pixel detectors**

| Sensor cross-section → Parameter ↓ | charge signal CMOS electronics  p+ pw nw p+ deep nwell  p - substrate                                                                                                                             | charge signal CMOS electronics  n+ pw nw n+ deep pwell p - substrate                                                                                                                          |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                               | Large fill-factor (HV/HR-CMOS)                                                                                                                                                                    | Small fill-factor (HR-CMOS)                                                                                                                                                                   |  |

| 1) p/n junction                    | p-substrate/large deep n-well (RO in charge collection well)                                                                                                                                      | p-substrate/small shallow n-well (RO outside charge collection well)                                                                                                                          |  |

| 2) Substrate biasing               | High voltage                                                                                                                                                                                      | Low voltage                                                                                                                                                                                   |  |

| 3) Substrate resistivity           | < 2-3 kΩ·cm                                                                                                                                                                                       | < 8 kΩ·cm                                                                                                                                                                                     |  |

| 1) + 2) + 3)                       | <ul> <li>Large pixel capacity</li> <li>Higher noise</li> <li>Higher power consumption</li> <li>Short drift distances</li> <li>High radiation tolerance</li> <li>Good timing resolution</li> </ul> | <ul> <li>Small pixel capacity</li> <li>Lower noise</li> <li>Low power consumption</li> <li>Long drift distances</li> <li>Less radiation tolerance</li> <li>Worse timing resolution</li> </ul> |  |

| Process                            | AMS/TSI 180 nm + LFoundry 150 nm                                                                                                                                                                  | TowerJazz 180 nm                                                                                                                                                                              |  |

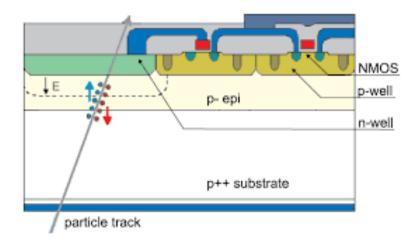

### Monolithic pixel detectors: CMOS

- Sensor and readout electronics on single wafer in standard CMOS (low-voltage CMOS)

- Reduced material thickness (50 μm)

- Small pixel size (18 μm x 18 μm)

- In-pixel signal amplification

- More cost effective (~£100k/m²)

- Small bias voltage (V<sub>bias</sub>)

- Slow charge collection by diffusion (2 μs)

- Limited radiation tolerance (10<sup>13</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>)

- State-of-the-art for high precision experiments

Improved values recently

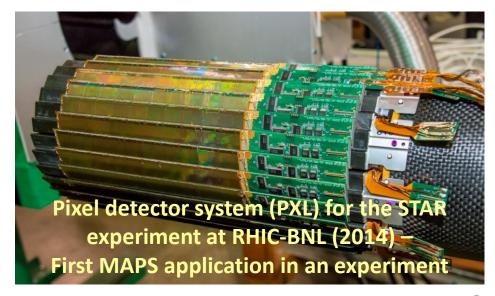

### **CMOS** detectors in particle physics – STAR experiment

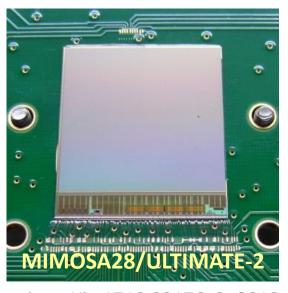

#### MIMOSA-28 / ULTIMATE chip:

G. Contin, arXiv:1710.02176v2, 2018

Chip size20 mm x 22 mm

Total detector area

0.15 m<sup>2</sup>

Sensor matrix

928 x 960 pixels (~0.9 Mpixels per chip); 400 pixel chips in total ~360 Mpixels

– Pixel size  $20.7 \mu m$  x  $20.7 \mu m$  (MAPS chosen to improve hit resolution to enable the

reconstruction of hadronic decays of heavy flavour mesons and baryons)

- Radiation tolerance 150 krad (TID) +  $10^{12}$  1 MeV  $n_{eq}$ /cm<sup>2</sup> (NIEL)

– Process AMS 0.35 μm OPTO

### **CMOS** detectors in everyday life

#### The best camera phone in 2022

(Image credit: Basil Kronfli / Digital Camera World)

#### 1. Samsung Galaxy S22 Ultra ★★★★

With a built-in stylus this is the best Android camera phone

#### SPECIFICATIONS

Release date: February 2022

Rear cameras: 108MP f/1.8, 10MP f/2.4, 10MP f/4.9

12MP f/2.2 ultrawide

Front camera: 40MP OIS: Yes Weight: 228 g

Dimensions: 163.3 x 77.9 x 8.9 mm

Storage: 128GB/256GB/1TB

#### Galaxy S22 Ultra

Quad camera

- 12MP Ultra Wide Camera

- Dual Pixel AF

- Pixel size: 1.4µm

- FOV: 120°

- F.No (aperture): F2.2

- 1/2.55" image sensor size

- 2 108MP Wide-angle Camera

- PDAF, OIS

- Pixel size: 0.8μm (12MP 2.4μm)

- FOV: 85°

- F.No (aperture): F1.8

- 1/1.33" image sensor size

- 3 10MP Telephoto Camera

- Dual Pixel AF

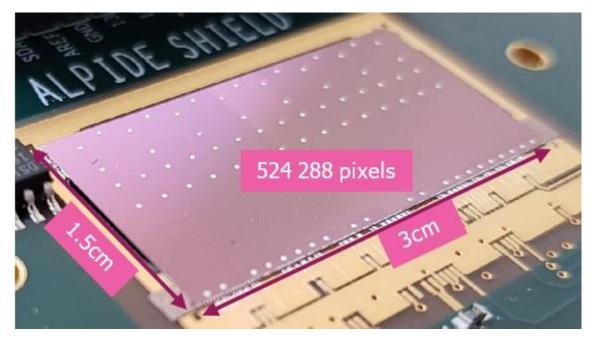

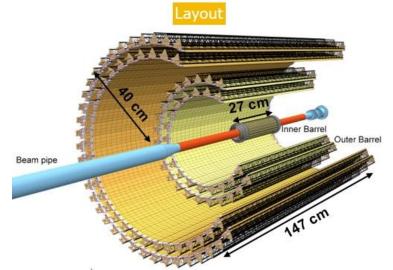

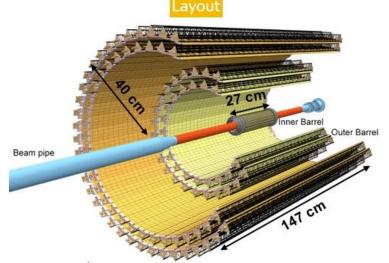

### **CMOS** detectors in particle physics – ALICE ITS upgrade

**ALICE ITS upgrade ITS2 (2020)**

#### **Sensor requirements**

| Parameter                                  | IB                   | ОВ               |

|--------------------------------------------|----------------------|------------------|

| Sensor thickness (μm)                      | 50                   | 50               |

| Spatial resolution (μm)                    | 5                    | 10               |

| Dimensions (mm²)                           | $15 \times 30$       | $15 \times 30$   |

| Power density (mW cm <sup>-2</sup> )       | 300                  | 100              |

| Time resolution (μs)                       | 30                   | 30               |

| Detection efficiency (%)                   | 99                   | 99               |

| Fake hit rate <sup>a</sup>                 | 10 <sup>-5</sup>     | 10 <sup>-5</sup> |

| TID radiation hardness <sup>b</sup> (krad) | 2700                 | 100              |

| NIEL radiation hardness <sup>b</sup>       | $1.7 \times 10^{13}$ | 10 <sup>12</sup> |

| $\left(1{ m MeV}n_{ m eq}/{ m cm}^2 ight)$ |                      |                  |

M. Mager, doi.org/10.1016/j.nima.2015.09.057, 2016

### **CMOS** detectors in particle physics – ALICE ITS upgrade

**ALPIDE**

#### **ALICE ITS upgrade ITS2 (2020)**

#### ALPIDE chip:

Chip size15 mm x 30 mm

Total detector area

10 m<sup>2</sup>

Sensor matrix

1024 x 512 pixels (> 0.5 Mpixels); 24k pixel chips in total ~12.5 Gpixels

– Pixel size 26 μm x 29 μm

Radiation tolerance 700 krad (TID)

$10^{13}$  1 MeV  $n_{eq}$ /cm<sup>2</sup> (NIEL)

ProcessTowerJazz 180 nm

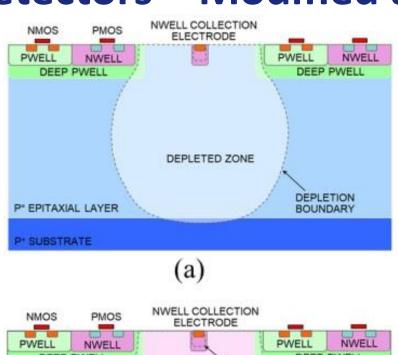

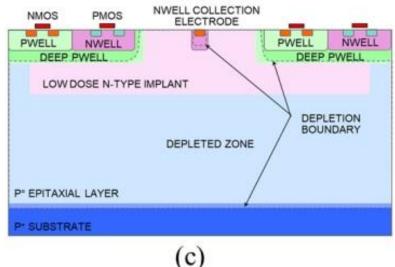

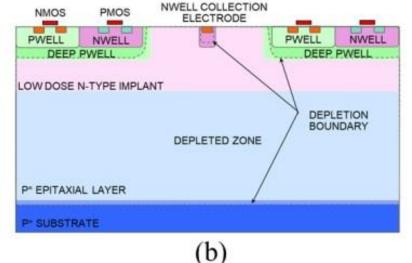

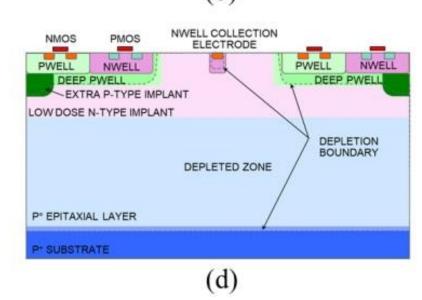

### **CMOS** detectors – Modified and improved TowerJazz

**Process** modifications to fully deplete the sensor and enhance the lateral electric field in the pixel corners for good tolerance to NIFI (Non-Ionising Energy Loss)

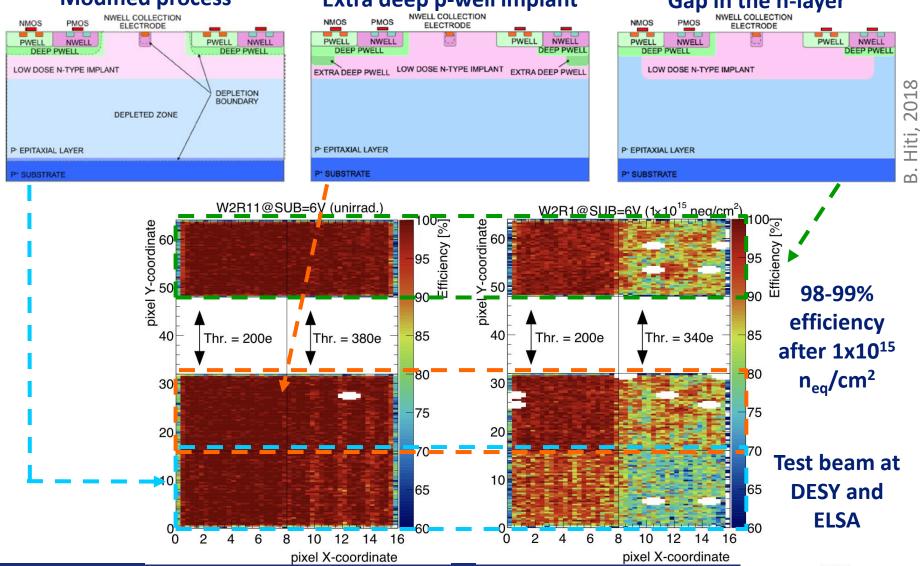

# CMOS detectors - Modified and improved TowerJazz Modified process Extra deep p-well implant Gap in the n-layer

Implemented in

MALTA chips

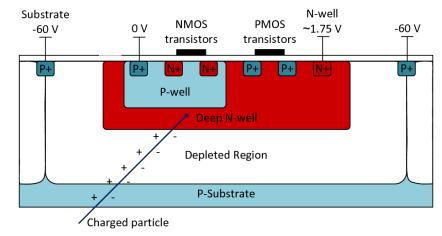

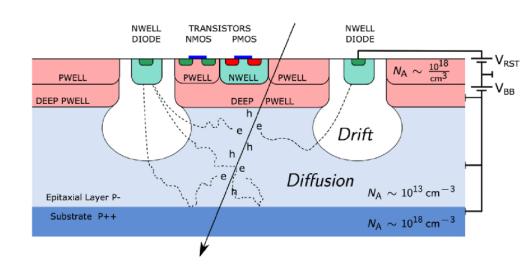

### Monolithic pixel detectors: HV-CMOS

- Sensor and readout electronics on single wafer in standard High Resistivity/High Voltage-CMOS (HR/HV-CMOS)

- Reduced material thickness (50 μm)

- Small pixel size (50 μm x 50 μm)

- In-pixel amplification

- More cost effective (~£100k/m²)

- Larger bias voltage (V<sub>bias</sub>)

- Fast charge collection by drift (~3 ns time resolution)

- Good radiation tolerance (10<sup>15</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>)

- One limitation: The chip size is in principle limited to 2 cm x 2 cm,

although stitching options are being investigated

- Next generation

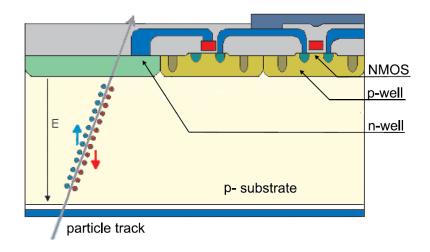

### Monolithic pixel detectors: HV-CMOS

- HV-CMOS processes originally used for driving automotive or industrial devices

- 2007  $\rightarrow$  First publication of a HV-CMOS detector chip (test chip in 0.35 µm HV-CMOS process from AMS)

- Small pixel matrix

- Pixels = Sensor + pixel electronics (CSA, discriminator and digital storage)

- Pixel electronics in the deep n-well

- Successful measurements with X-ray and beta radioactive sources

- HV contacts at the top side

- HV-CMOS processes are attractive for particle physics because

- Silicon bulk biased at high voltage (e.g. -100 V)

- Multiple nested wells to isolate the low-voltage CMOS readout electronics from the bulk

- Commercially available (i.e. fabrication is low-cost and reliable, there is availability of multiple vendors and large scale production)

I. Peric, NIM-A: 582 876-885, 2007

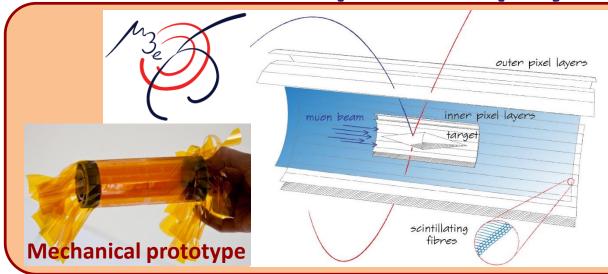

### **HV-CMOS** detectors in particle physics

- First HV-CMOS application in an experiment (202x)

- Requirements:

- Low material 50 μm

- Good time resolution< 20 ns (for pixels)</li>

- Fine segmentation 80 μm x 80 μm

## **HV-CMOS** detectors in particle physics – Mu3e

| Prototype | Year | Active area (mm²) | Functionality                                           | Main features                                                          |

|-----------|------|-------------------|---------------------------------------------------------|------------------------------------------------------------------------|

| MuPix1    | 2011 | 1.77              | Sensor + analog RO                                      | First MuPix prototype                                                  |

| MuPix2    | 2011 | 1.77              | Sensor + analog RO                                      |                                                                        |

| MuPix3    | 2012 | 9.42              | Sensor + analog/digital RO                              | First digital RO                                                       |

| MuPix4    | 2013 | 9.42              | Sensor + analog/digital RO                              | Working digital RO and time-<br>stamping                               |

| MuPix6    | 2013 | 10.55             | Sensor + analog/digital RO                              |                                                                        |

| MuPix7    | 2014 | 10.55             | SoC (all relevant features for a fully monolithic chip) | First MuPix with SM, clock generation and fast serial RO (1.25 Gbit/s) |

| MuPix8    | 2017 | 160               | Large SoC                                               | First large MuPix prototype, with TW correction                        |

| MuPix9    | 2018 |                   | SoC                                                     | Voltage regulators                                                     |

| MuPix10   | 2019 | 400               | Full size (reticle) SoC                                 | First full size SoC                                                    |

| MuPix11   | 2022 |                   | Full size (reticle) SoC                                 | Fixes bugs of MuPix10                                                  |

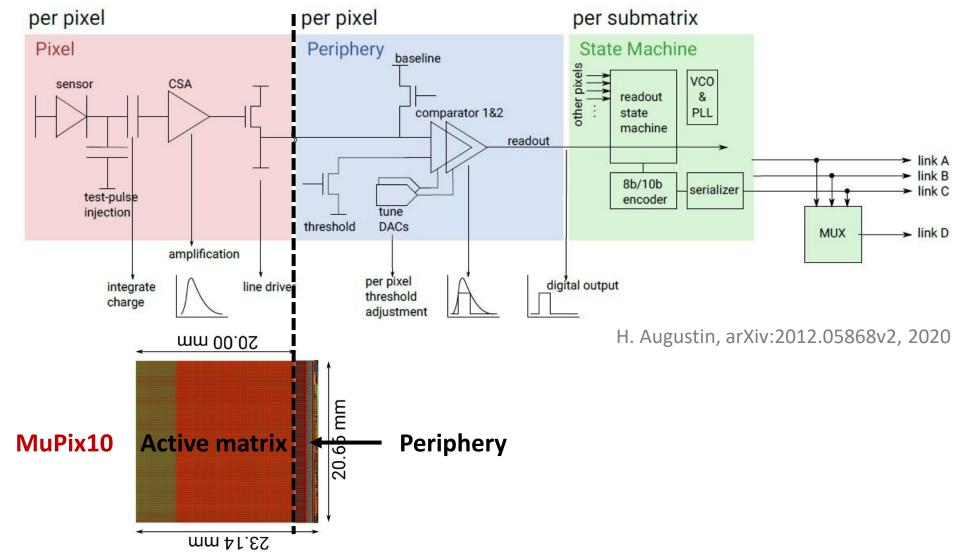

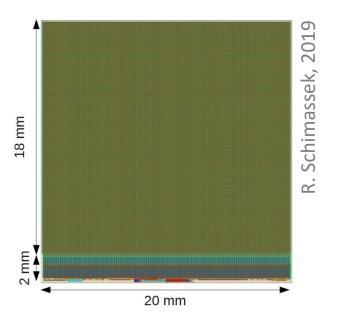

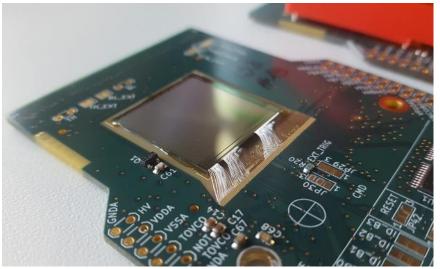

#### MuPix10 – Main details

- Fully monolithic sensor in the 180 nm HV-CMOS TSI process

- Active pixel matrix size of 20 mm x 20 mm (256 x 250 pixels)

- Chip split into 3 sub-matrices with 84, 86 and 86 columns

- Pixel size is 80 μm x 80 μm

- Hits are read out using the column-drain architecture

- Two time-stamps are stored for each hit (rising and falling edges)

- 8b10b encoding

- Hits are sent over up to four serial links with nominal 1.25 Gbit/s

- One link per sub-matrix + an additional fourth to send combined data

- Max. hit rate of 90 Mhit/s can be achieved, theoretically

- On-chip biasing to minimise electrical connections

- Measured V\_BD = 100 V, 200  $\Omega$ ·cm substrate resistivity  $\rightarrow$  W\_D = 40  $\mu$ m

- No inactive bulk for 50 μm thin sensors

- Measured power consumption = 190 mW/cm²

H. Augustin, Tracking Verbund Meeting, 2021

### **MuPix – Functional diagram**

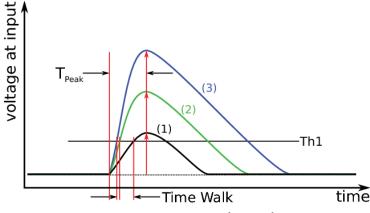

# Time-Walk (TW) – What is it & ways to improve it

#### Time-Walk (TW)

What is it? Variation of the response time of the readout electronics depending on the number of e<sup>-</sup>/h<sup>+</sup> pairs collected by the sensor

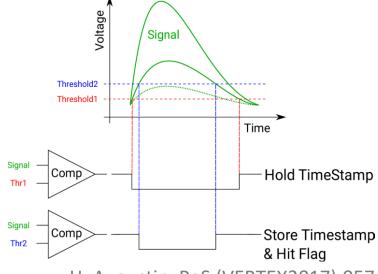

#### TW correction - Two-threshold method

- Two comparators with two threshold voltages:

- VTH1 is very low (close to the noise level) → it delivers a time-stamp with small TW

- VTH2 > VHT1 → it confirms that the flagged time-stamp corresponds to a real signal and not to noise

- Measured results show the TW can be reduced to ~3 ns

#### <u>TW correction</u> – <u>Other methods</u>

- Increasing the response rate of the amplifier (CACTUS, RD50-MPW2)

- Time-walk compensated comparator (HVStripV1, H35DEMO)

- Sampling method (LF-ATLASPix, CERN-RD50)

R. Schimassek, IEEE NSS/MIC/RTSD, 2016

H. Augustin, PoS (VERTEX2017) 057

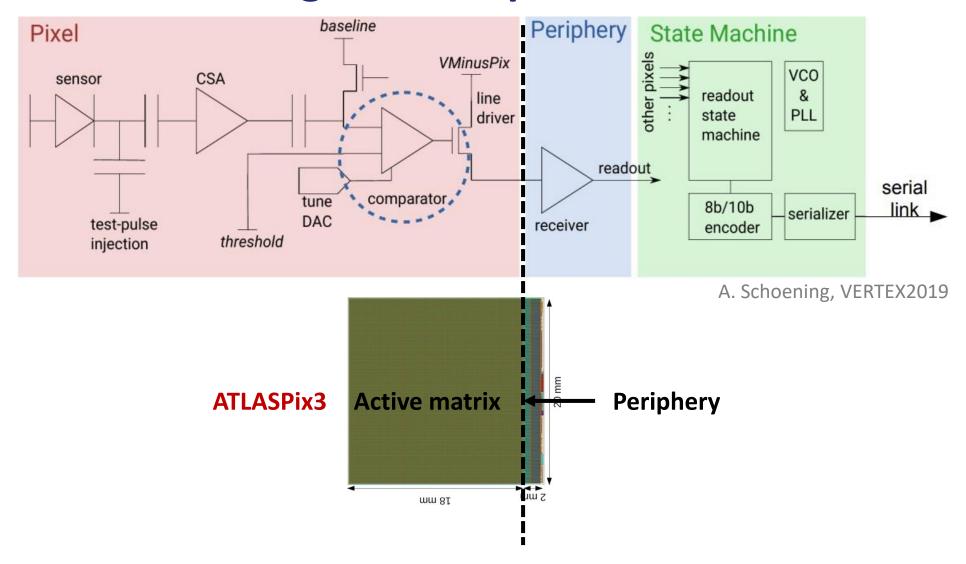

# Other functional diagrams are possible

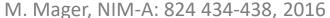

#### **HV-CMOS** detectors – ATLASPix3

ATLASPix3 – Some chip details

- Matrix with 132 columns x 372 rows

- 150 μm x 50 μm pixel size

- Trigger latency ≤ 25 μs

- Radiation hard design

- Serial powering (only one power supply needed)

- Data interface is very similar to ATLAS RD53 readout chip

- Power consumption is ~200 mW/cm<sup>2</sup> (with 25 ns time resolution)

ATLASPix3 is the first full reticle pixel detector (2 cm x 2 cm) compatible with ATLAS ITk L4 requirements

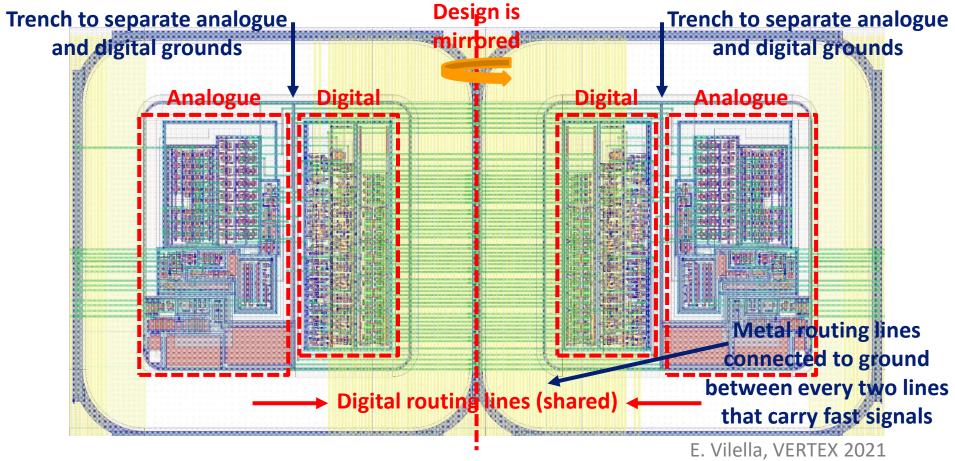

### Other functional diagrams are possible

- Double column scheme to alleviate routing congestion and minimise crosstalk

- Pixels within double column share many signals  $\rightarrow \sim x0.5$  less routing lines

- Shared signals are digital input/outputs (TS IN, TS OUT, ADDR), control signals (Read, Freeze, etc.)

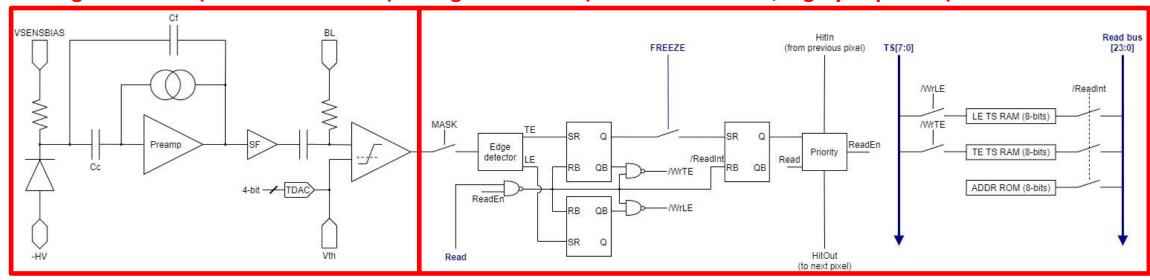

#### **RD50-MPW3 – Pixel schematic**

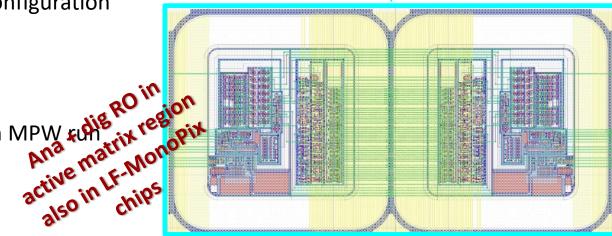

Analogue readout (from RD50-MPW2) Digital readout (from RD50-MPW1, highly improved)

- Each pixel receives global 8-bit Time-Stamp (TS) and returns

- 8-bit TS leading edge + 8-bit TS falling edge

- 8-bit pixel address

- Each pixel integrates 8-bit SRAM shift register for serial configuration (not shown in diagram)

- Pixel-trimming to compensate for threshold voltage variations (4-bits)

- Flag to mask noisy pixels (1-bit)

- Signals to enable/disable calibration circuit (1-bit), SF output (1-bit), COMP output (1-bit)

- Pixels implemented in a double column (DCOL) scheme with shared routing lines to minimise congestion

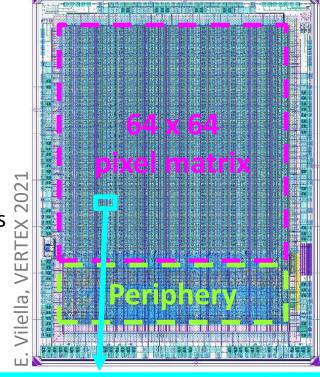

#### **RD50-MPW3 – Main details**

- **RD50-MPW2** very successful chip, but with limitations

- Pixel matrix with reduced number of rows and columns (8 x 8)

- No pixel digital readout to identify particle hits

- Very simple TX readout  $\rightarrow$  some measurements too slow or not possible

- **RD50-MPW3** has larger and more advanced matrix to further study HV-CMOS sensors

- 64 rows x 64 columns (chip size is 5.1 mm x 6.6 mm)

- Analogue readout taken from RD50-MPW2

- In-pixel digital readout (FE-I3 style)

- Pixel size is 62 μm x 62 μm

- Optimised peripheral readout for effective pixel configuration and fast data TX

- Power grid to avoid IR drops

- With all the lessons learned from RD50-MPW1/2

- RD50-MPW3 submitted in December 2021 through an MPW suffer Delivery expected in late May early lung 2022

- Delivery expected in late May early June 2022

- Substrate resistivities: standard, 1.9k and >2k  $\Omega$ ·cm

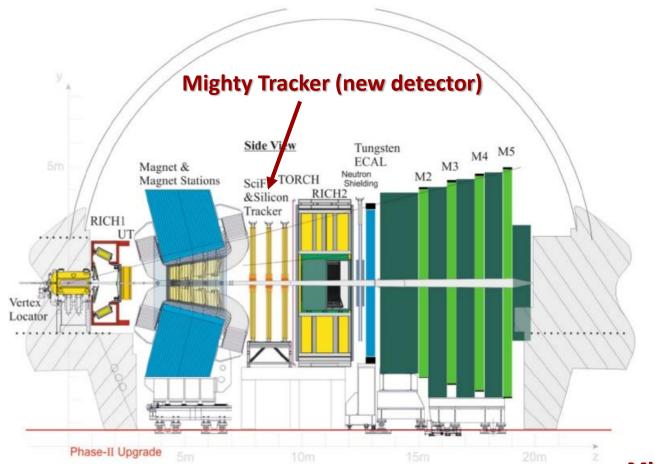

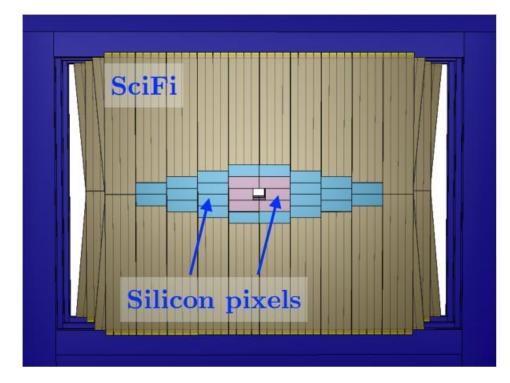

### **HV-CMOS** detectors in particle physics – Mini-quiz

#### 2028/2030+

- An experiment is proposing a new detector for its next upgrade

- Requirements:

- Excellent time resolution 3 ns

- Pixel size of approximately 50 μm x 150 μm

- Radiation tolerance 3·10<sup>14</sup> 1MeV n<sub>eq</sub>/cm<sup>2</sup>

What detector would you use? Can you guess the experiment?

### **HV-CMOS** detectors in particle physics – LHCb

MightyPix1 is being submitted, as we speak, to TSI First HV-CMOS sensor with almost compatible LHCb interface

# Thank you for your attention