### Introduction into Electronics

- (1) Reminder: Electrical circuits

- (2) Analog electronics

- (3) Digital electronics

- (4) Circuit analysis, circuit topologies

### Introduction into Electronics

(1) Reminder: Electrical circuits

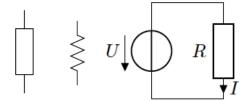

### Basic elements

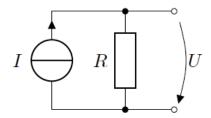

Power source:

DC voltage source:

DC current source:

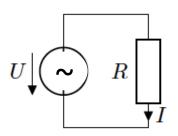

AC source:

$$U(t) = U_0 \sin(\omega t)$$

$$\hat{U} = U_{eff} = U_0 / \sqrt{2}$$

**Resistance:**

$U = R \cdot I.$

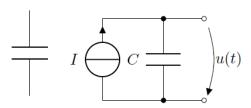

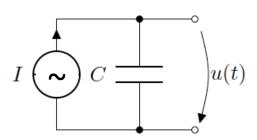

**Capacitance:**

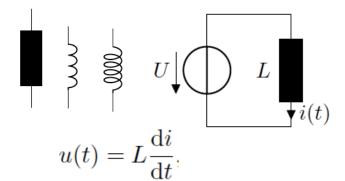

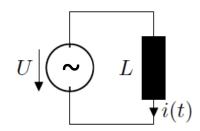

**Inductance:**

$$Q = C \cdot U$$

$$Q = C \cdot U$$

$i(t) = \frac{\mathrm{d}q}{\mathrm{d}t} = C \cdot \frac{\mathrm{d}u}{\mathrm{d}t}$

### AC resistance

#### **Resistance:**

$$I_R = rac{U_R}{R}$$

Rotation of phasors at rate  $\omega_a$

$U_R$

$U_R$

$U_{R,m}$

#### Capacitance:

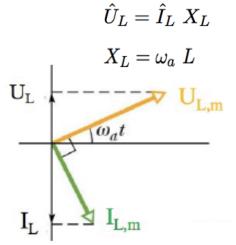

$$\hat{U}_C = \hat{I}_C \ X_C$$

$X_C = \frac{1}{\omega_a \ C}$

$I_{C,m}$

$I_C$

Rotation of phasors at rate  $\omega_a$

$U_C$

$U_{C,m}$

#### **Inductance:**

### Networks (more later)

# **Junction rule:**

#### **Loop rule**

$$\sum_{k=0}^{n} U_k = 0$$

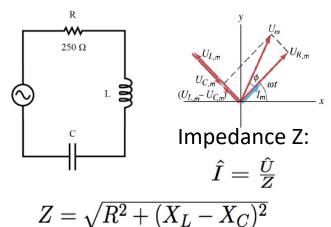

#### Impedance in AC circuits

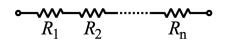

#### **Resistance in series:**

$$R_{\text{total}} = R_{\text{s}} = R_1 + R_2 + \dots + R_n$$

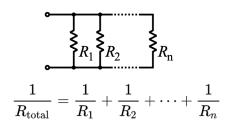

#### **Resistance in parallel:**

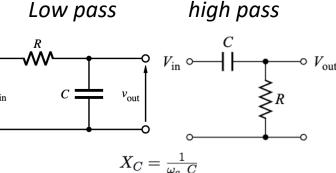

#### Low pass

### (2) Analog electronics

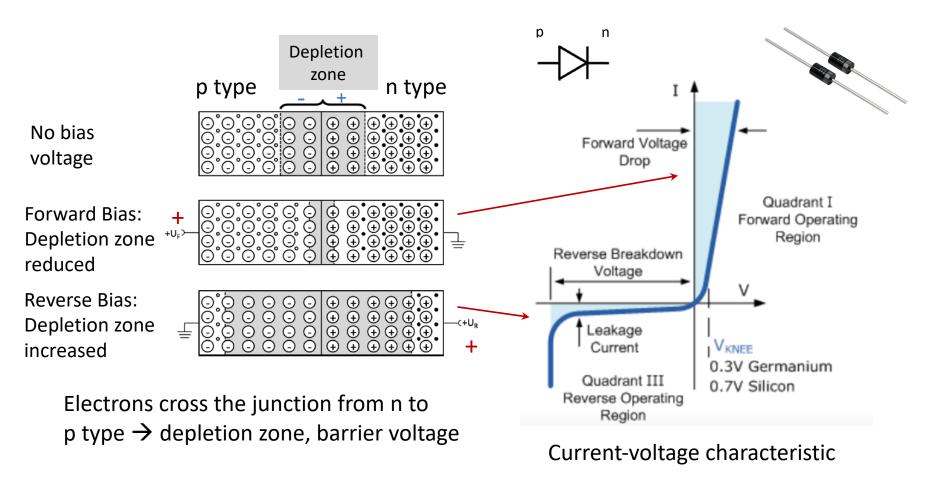

### Diode: pn junction and biasing

### Diode: forward biasing

#### Ideal diode (forward bias):

$$I(U) = I_{\mathrm{S}} \cdot \left(e^{\frac{U}{U_{\mathrm{T}}}} - 1\right)$$

$I_S$ : leakage current  $\approx$  1-100 μA  $U_T$ : = kT/e  $\approx$  40 mV

#### Real diode (forward bias):

I(U) only > 0 for U > Barrier Voltage (  $\approx$  0.3-0.8V)

#### **Differential resistance:**

$$r = \frac{dI}{dU}$$

Current-voltage characteristic

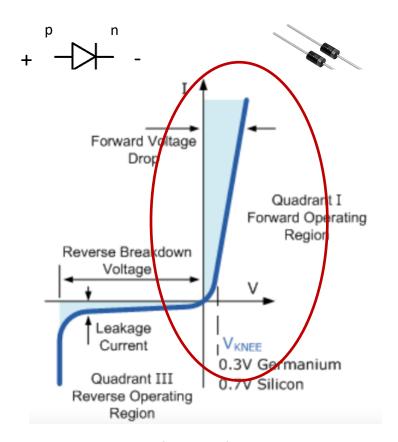

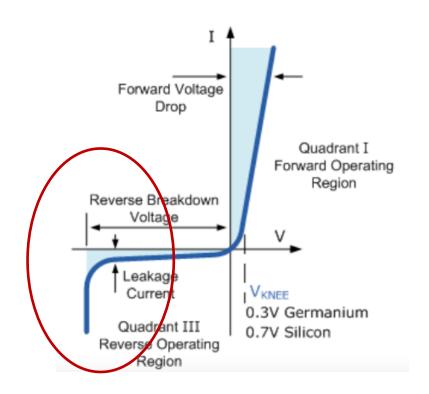

### Zener diodes: reverse biasing

Conventional diodes will typically be destroyed if operated with large reverse-bias voltages.

But a Zener diode is designed to be operated with reverse bias.

Resistance breaks down at the Zener voltage: tunneling of electrons From the p-type valence band into the n-type conduction band

→ Voltage stabilizer, reference voltage

### Circuits with diodes (1)

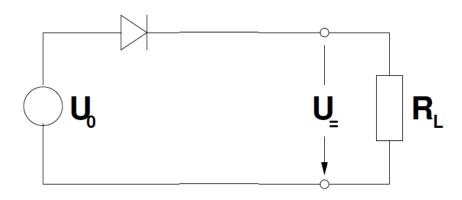

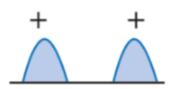

#### Half-wave rectifier

#### Blocks negative half waves

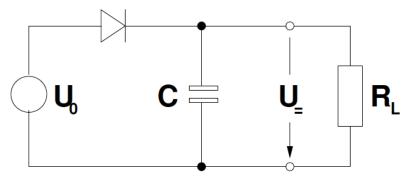

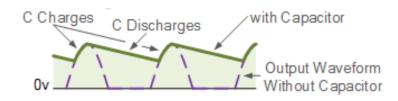

#### Half-wave rectifier with smoothing capacitor

#### Half waves smoothened

# Circuits with diodes (2)

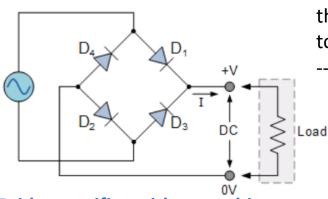

#### **Full-wave Bridge rectifier**

Diodes are arranged such that the positive pole is always connected to the same point.

--> Inverts negative half waves

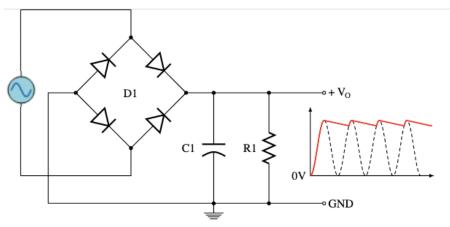

#### **Bridge rectifier with smoothing capacitance**

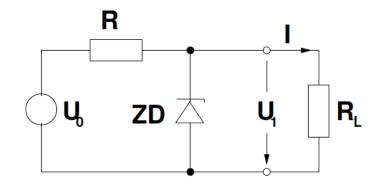

#### **Voltage regulation/limitation:**

If the initial voltage becomes larger than the Zener voltage the Zener current Increases → resistance drops

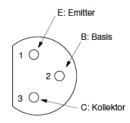

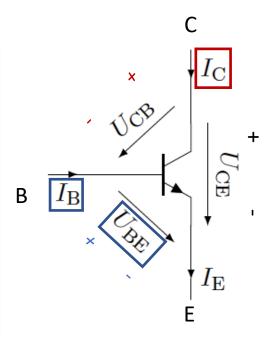

### **Transistors**

- Active, controllable semiconductor devices.

- Amplify and switch signals and power

- o Main types:

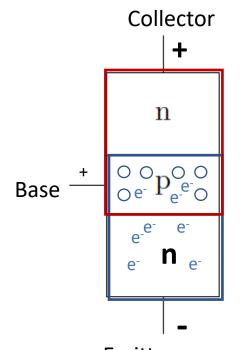

- Bipolar junction transistor (BJT)

- o here: npn transistor

- pnp transistor: works in an analogous manner

- MOSFET: NMOS/PMOS

- CMOS: combines NMOS an PMOS

Contemporary Integrated Circuits (IC) are in general not build from discrete transistors but need to understand the transistor principle to understand IC

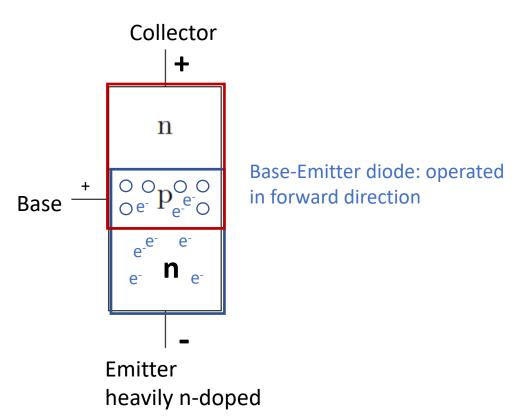

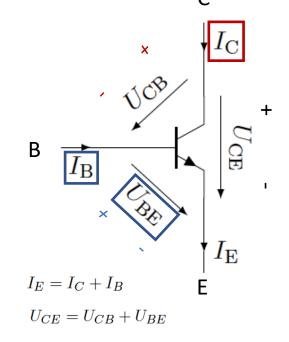

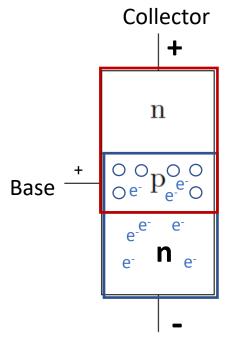

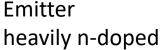

Base-Collector diode: operated in reverse bias

→ "leakage" collector current I<sub>C</sub>

Base-Emitter diode: operated in forward direction

heavily n-doped

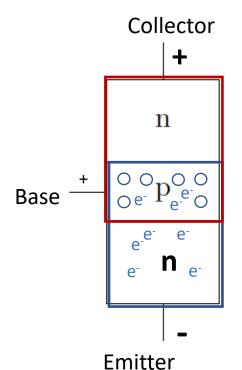

Base-Collector diode: operated in reverse bias

→ "leakage" collector current I<sub>C</sub>

Base-Emitter diode: operated in forward direction

- → electrons drift into the base

- → some electrons reach the p-n transition region of the Base-Collector diode

- → increase collector current I<sub>C</sub>

Base-Collector diode: operated in reverse bias

→ "leakage" collector current I<sub>C</sub>

Base-Emitter diode: operated in forward direction

- → electrons drift into the base

- → some electrons reach the p-n transition region of the Base-Collector diode

- → increase collector current I<sub>C</sub>

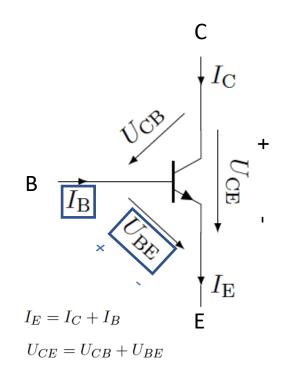

$$I_B/U_{BE} \rightarrow control \rightarrow I_C$$

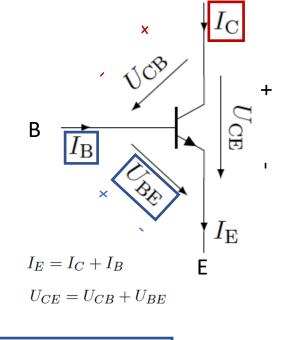

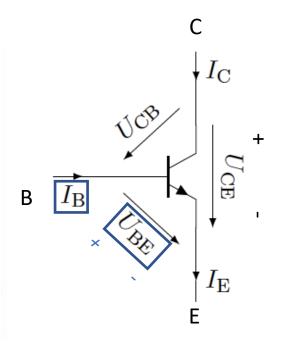

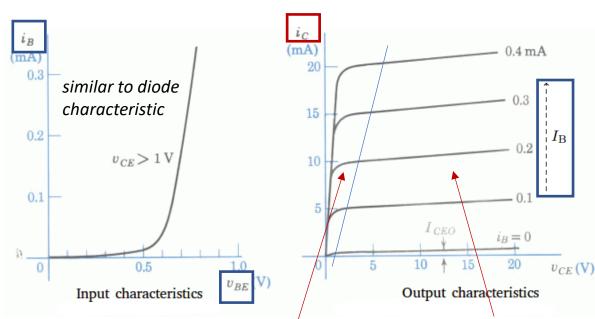

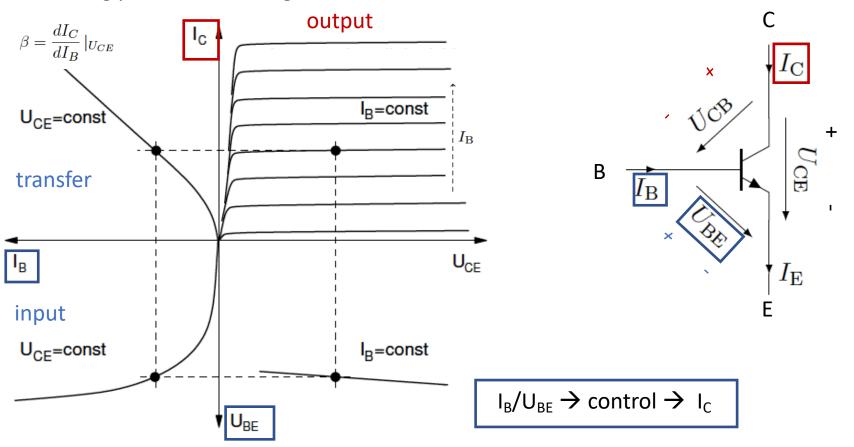

# npn BJT: characteristics (1)

#### Input characteristics

### npn BJT: characteristics (1)

#### Output characteristics

#### Saturation region:

Small changes in  $U_{CE}$  lead to large change in  $I_C$   $\rightarrow$  switches etc.

#### Active region:

Small change in base current  $I_B$  lead to large change in collector current, nearly independent of  $U_{CE}$   $\rightarrow$  Current amplification etc.

# npn BJT: characteristics (2)

working point in active region

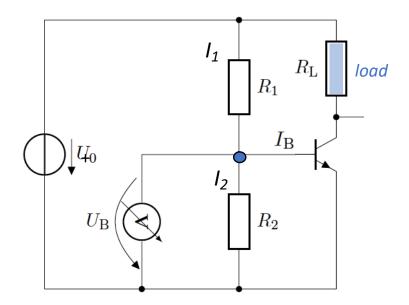

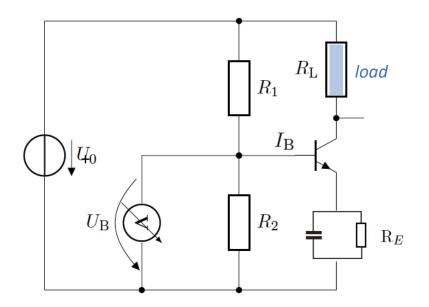

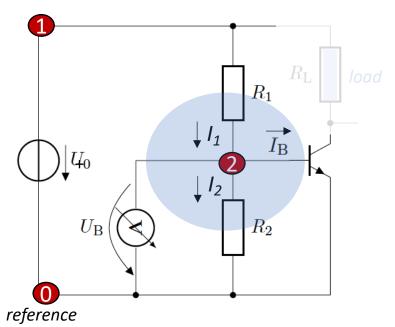

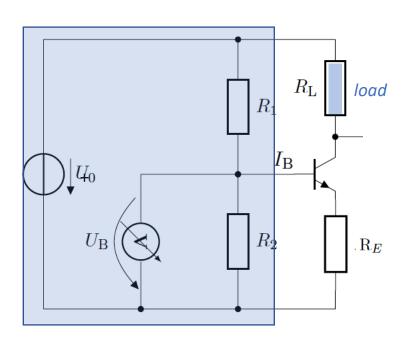

### Selecting the working point

#### Example circuit

(Calculation: see later)

#### Voltage divider biasing

The voltage U<sub>B</sub> across R<sub>2</sub> forward-biases the BE junction

$$U_B = U_0 \cdot \frac{R_2}{R_1 + R_2} - I_B \cdot \frac{R_1 R_2}{R_1 + R_2}$$

If R<sub>1</sub>, R<sub>2</sub> are sufficiently small, the base current does not impact the base voltage

$$I_B \cdot R_1 \ll U_0$$

$\rightarrow$   $U_B \approx U_0 \cdot \frac{R_2}{R_1 + R_2}$

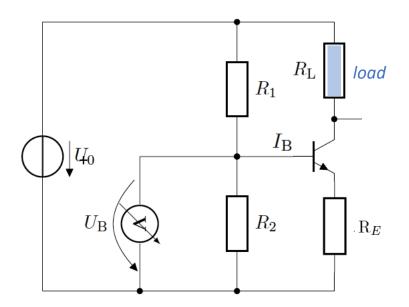

### Selecting the working point

#### Example circuit

#### Voltage divider biasing

The voltage U<sub>B</sub> across R<sub>2</sub> forward-biases the BE junction

$$U_B = U_0 \cdot \frac{R_2}{R_1 + R_2} - I_B \cdot \frac{R_1 R_2}{R_1 + R_2}$$

If R<sub>1</sub>, R<sub>2</sub> are sufficiently small, the base current does not impact the base voltage

$$I_B \cdot R_1 \ll U_0$$

$\rightarrow$   $U_B \approx U_0 \cdot \frac{R_2}{R_1 + R_2}$

Stabilizing WP by adding emitter resistance R<sub>E</sub>

Reduces U<sub>BE</sub> if base current I<sub>B</sub> becomes too large.

### Selecting the working point

#### Example circuit

#### Voltage divider biasing

The voltage U<sub>B</sub> across R<sub>2</sub> forward-biases the BE junction

$$U_B = U_0 \cdot \frac{R_2}{R_1 + R_2} - I_B \cdot \frac{R_1 R_2}{R_1 + R_2}$$

If R<sub>1</sub>, R<sub>2</sub> are sufficiently small, the base current does not impact the base voltage

$$I_B \cdot R_1 \ll U_0$$

$\rightarrow$   $U_B \approx U_0 \cdot \frac{R_2}{R_1 + R_2}$

#### Stabilizing WP by adding emitter resistance R<sub>E</sub>

Reduces U<sub>BE</sub> if base current I<sub>B</sub> becomes too large.

Effect on AC signal can be mitigated by adding a capacitor in parallel

$\rightarrow$  R<sub>E</sub> || R<sub>C</sub> reduced for high frequencies, R  $\approx$  R<sub>E</sub> for low frequencies

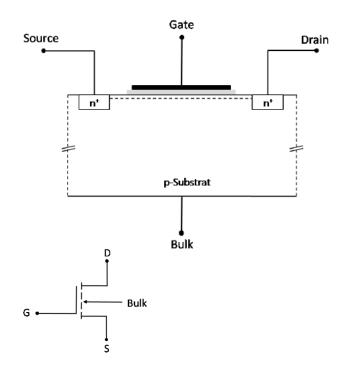

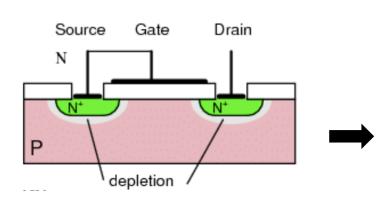

### FET

BJT not suited for Integrated Circuits (IC): base currents would overheat the IC

- → use FETs: similar operation as with BJT but:

- controlled with negligible currents

- o smaller area

- transfer characteristics more linear

- less noise

Example n-channel MOSFET (Metal-Oxide-Silicon FET):

- o p-doted substrate

- o n-doted channels: Source, Drain

- Gate isolated from substrate by e.g. SiO<sub>2</sub>

- → no Gate-Source/Drain currents

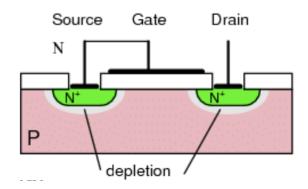

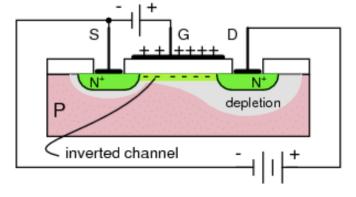

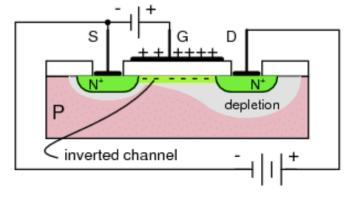

# N-channel MOSFET: operation

No source drain current

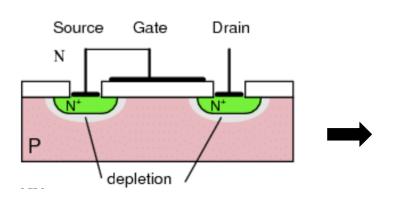

# N-channel MOSFET: operation

No source drain current

- Electrons from p-doted substrate drawn towards positively charged gate

- $\circ$   $\rightarrow$  channel allows for S-D current I<sub>D</sub>

# N-channel MOSFET: operation

- No source drain current

- output characteristic  $U_{GS}$

- Electrons from p-doted substrate drawn towards positively charged gate

- → channel allows for S-D current I<sub>D</sub>

Tipically smaller transconductance than BJT (output current /input voltage)

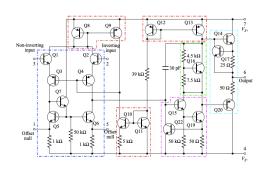

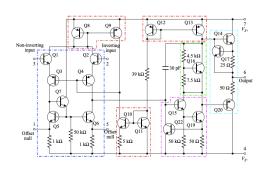

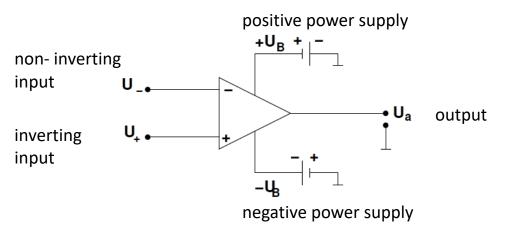

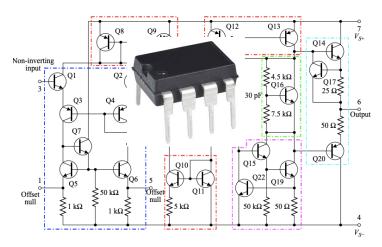

# Operational amplifier (op amp)

#### Difference amplifier with two inputs and one output

#### Characteristics:

- Output voltage proportional to the difference between the input voltages: very high amplification (> 10000-100000)

- o If used with negative feedback ( $U_a$  connected with  $U_a$ ) the op amp regulates  $U_a$  =  $U_a$  [1]

- Negligible input current (into the op amp) [2]

- The maximum output voltage is the power supply voltage

$$U_{\mathbf{a}} = v_0 \cdot (U^+ - U^-)$$

negative feedback

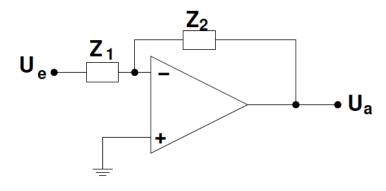

#### Inverting amplifier

[2]

$$\rightarrow$$

$I_1 = \frac{U_e - U^-}{Z_1} = \frac{U^- - U_a}{Z_2} = I_2$

[1]

$$\rightarrow U^- = 0 \text{ V}$$

(virtual ground)

$$\rightarrow U_{\rm a} = -\frac{Z_2}{Z_1} U_{\rm e}$$

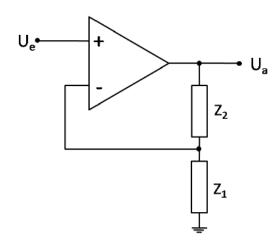

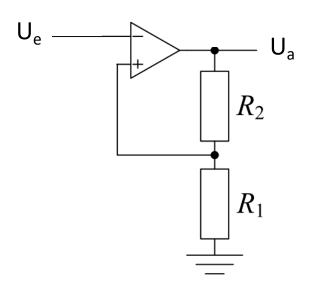

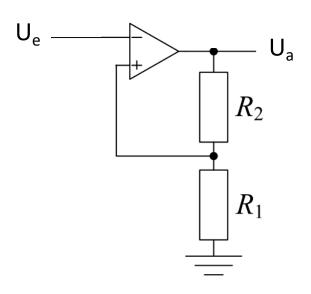

#### Non-inverting amplifier

Negative feedback from voltage divider:

[1]

$$\rightarrow U_e = U - = \frac{Z_1}{Z_1 + Z_2} U_a$$

$$\rightarrow U_a = \left(\frac{Z_2}{Z_1} + 1\right) U_e$$

- If used with negative feedback (U<sub>a</sub> connected with U-)

the op amp regulates U+ = U- [1]

- Negligible input current (into the op amp) [2]

28

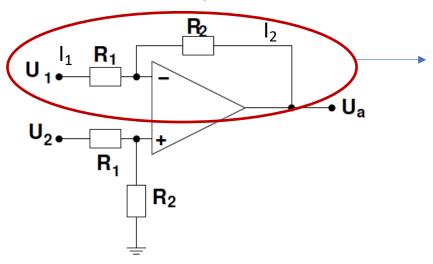

#### Differential amplifier

$$[1] U_{-} = U_{+} = U$$

[2]

$$I_1 = \frac{U_1 - U}{R1} = I_2 = \frac{U - U_a}{R2}$$

$$\Rightarrow \frac{U_1 R_2}{R_1} - \frac{U R_2}{R_1} = U - U_a$$

$$\rightarrow U_a = U \frac{R_2 + R_1}{R_1} - U_1 \frac{R_2}{R_1}$$

(\*)

- If used with negative feedback (U<sub>a</sub> connected with U-) the op amp regulates U+ = U- [1]

- Negligible input current (into the op amp) [2

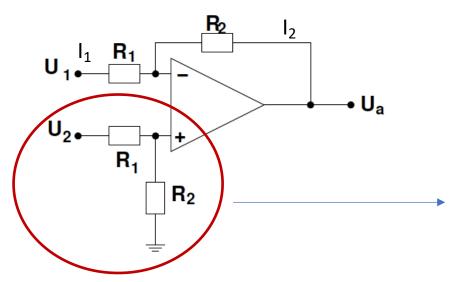

#### Differential amplifier

[1]

$$U_{-} = U_{+} = U$$

[2]

$$I_1 = \frac{U_1 - U}{R1} = I_2 = \frac{U - Ua}{R2}$$

$$\Rightarrow \frac{U_1 R_2}{R_1} - \frac{U R_2}{R_1} = U - Ua$$

$$\rightarrow U_a = U \frac{R_2 + R_1}{R_1} - U_1 \frac{R_2}{R_1}$$

(\*)

$$U = U_2 \frac{R_2}{R_1 + R_2}$$

(voltage divider) (\*\*)

- If used with negative feedback (U<sub>a</sub> connected with U-) the op amp regulates U+ = U- [1]

- Negligible input current (into the op amp) [2

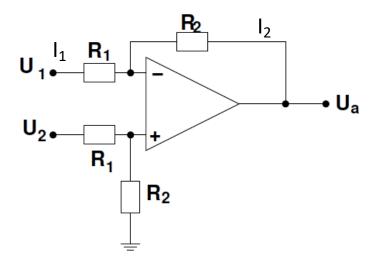

#### Differential amplifier

- If used with negative feedback (U<sub>a</sub> connected with U-) the op amp regulates U+ = U- [1]

- Negligible input current (into the op amp) [2

$$[1] \ U_{-} = U_{+} = U$$

[2]

$$I_1 = \frac{U_1 - U}{R1} = I_2 = \frac{U - Ua}{R2}$$

$$\Rightarrow \frac{U_1 R_2}{R_1} - \frac{U R_2}{R_1} = U - Ua$$

$$\rightarrow U_a = U \frac{R_2 + R_1}{R_1} - U_1 \frac{R_2}{R_1}$$

(\*)

$$U=U_2\,rac{R_2}{R_1+R_2}$$

(voltage divider) (\*\*)

(\*\*) in (\*)

$$\rightarrow U_a = U_2 \frac{R_2}{R_1 + R_2} \frac{R_1 + R_2}{R_1} - U_1 \frac{R_2}{R_1}$$

$$\rightarrow$$

$U_{\rm a} = \frac{R_2}{R_1} (U_2 - U_1)$

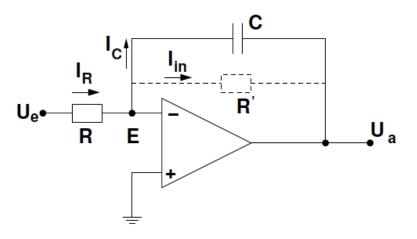

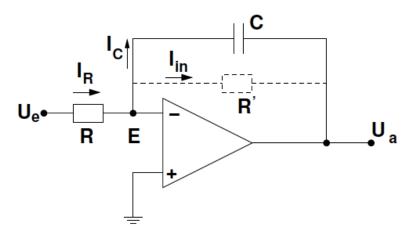

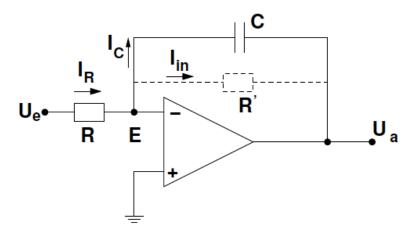

#### Integrator

→ op amp passes a current that charges the capacitor to maintain the virtual ground

$$I_R = \frac{U_e}{R} \approx I_c$$

#### Integrator

→ op amp passes a current that charges the capacitor to maintain the virtual ground

$$I_R = \frac{U_e}{R} \approx I_c$$

#### Capacitor equation:

- Differential:  $I = C \frac{dU}{dt}$

- Integrated:  $U = \frac{1}{C} \int I dt$  (\*)

#### Integrator

Capacitor equation:

- Differential:  $I = C \frac{dU}{dt}$

- Integrated:  $U = \frac{1}{C} \int I dt$  (\*)

→ op amp passes a current that charges the capacitor to maintain the virtual ground

$$I_R = \frac{U_e}{R} \approx I_c$$

with(\*):

$$U_a = -\frac{1}{RC} \int_0^t U_e \, dt$$

→ The output voltage is proportional to the time integrated input voltage

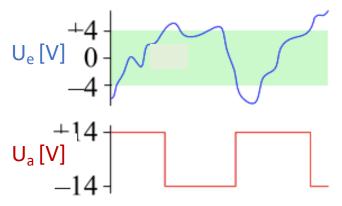

#### Schmitt trigger: positive feedback

If U<sub>a</sub> rises, the difference between U<sub>1</sub> and U<sub>+</sub> will rise. This causes U<sub>a</sub> to rise even further until maximum output voltage (given by the power supply voltage) is reached

$$U_{\mathbf{a}} = v_0 \cdot (U^+ - U^-)$$

#### Schmitt trigger: positive feedback

$$U_{\mathbf{a}} = v_0 \cdot (U^+ - U^-)$$

If  $U_a$  rises, the difference between  $U_a$  and  $U_+$  will rise. This causes  $U_a$  to rise even further until maximum output voltage (given by the power supply voltage) is reached

Example:

$$U_{max}$$

= 14V,  $R_1$  = 10 $\Omega$ ,  $R_2$  = 4 $\Omega$

If  $U_a$  = 14V, U+ = 4V. If  $U_e$  exceeds 4V,  $U_- > U_+$  and  $U_a$  flips to -14V

### (3) Digital electronics

## Digital electronics

Work with only two voltage levels (depend on type and input/output)

- High: 1, typically 2-5V

- Low: 0, typically 0-1.5V

#### Hexadecimal 4-bit groups:

| 0000 | 0 | 0100                         | 4 | 1000 | 8 | 1100 | $\mathbf{C}$ |

|------|---|------------------------------|---|------|---|------|--------------|

| 0001 | 1 | 0101                         | 5 | 1001 | 9 | 1101 | D            |

| 0010 | 2 | 0110                         | 6 | 1010 | A | 1110 | $\mathbf{E}$ |

| 0011 | 3 | 0100<br>0101<br>0110<br>0111 | 7 | 1011 | В | 1111 | $\mathbf{F}$ |

#### Example:

- o Decimal: 2022

- o Binary: 0000 0111 1110 0110

- Hexadecimal: 07E6

#### Boolean algebra

AND OR

| $\boldsymbol{x}$ | y | $x \wedge y$ | xee y |  |

|------------------|---|--------------|-------|--|

| 0                | 0 | 0            | 0     |  |

| 1                | 0 | 0            | 1     |  |

| 0                | 1 | 0            | 1     |  |

| 1                | 1 | 1            | 1     |  |

**NOT**

| x | eg x |  |  |

|---|------|--|--|

| 0 | 1    |  |  |

| 1 | 0    |  |  |

#### Laws:

- Associativity

- Commutativity

- Distributivity

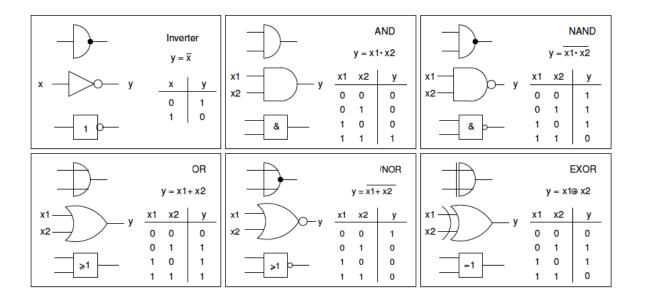

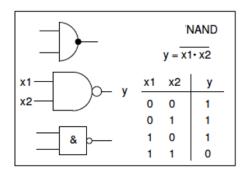

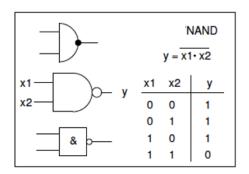

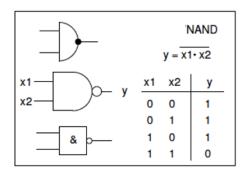

# Logical operations

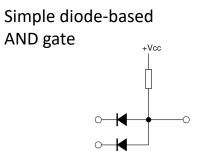

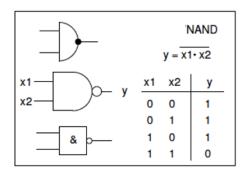

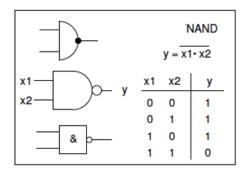

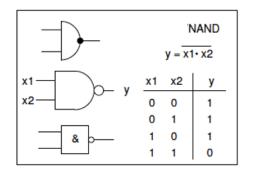

### Full table of symbols, including secondar operations

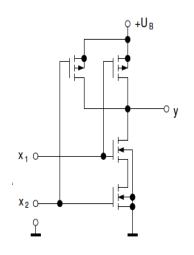

#### CMOS-based NAND gate

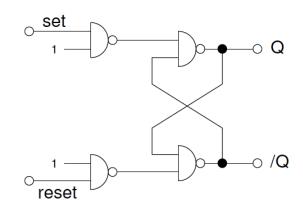

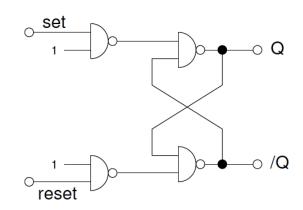

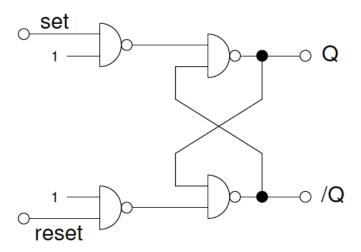

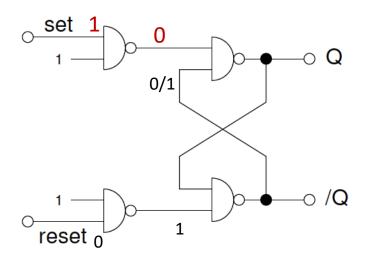

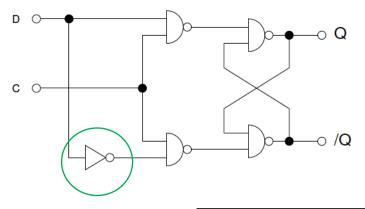

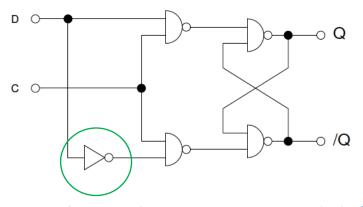

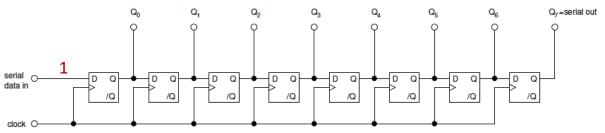

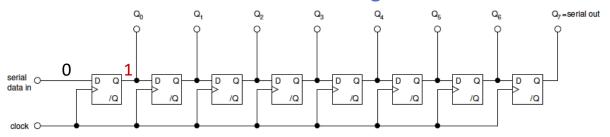

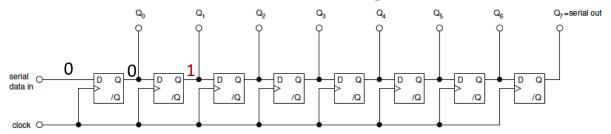

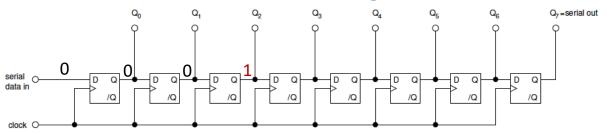

Flip flops (latches) are digital circuits with two stable states → store information

Flip flops (latches) are digital circuits with two stable states → store information

Flip flops (latches) are digital circuits with two stable states → store information

Flip flops (latches) are digital circuits with two stable states → store information

Flip flops (latches) are digital circuits with two stable states → store information

Flip flops (latches) are digital circuits with two stable states  $\rightarrow$  store information

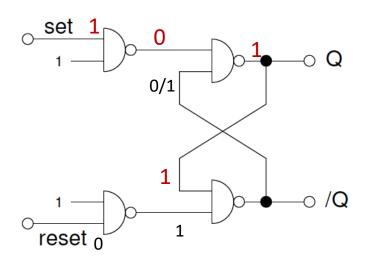

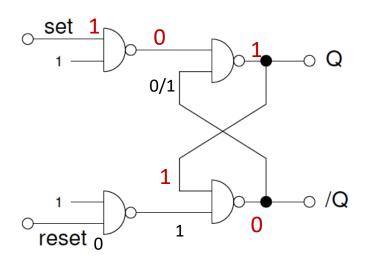

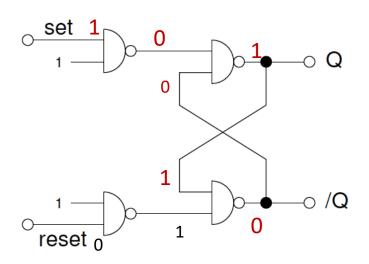

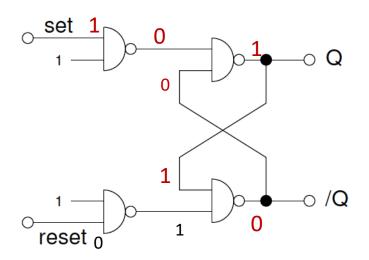

### Simple SR Latch

stable situation

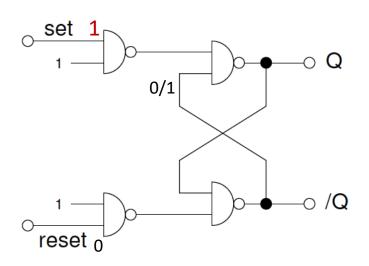

Flip flops (latches) are digital circuits with two stable states  $\rightarrow$  store information

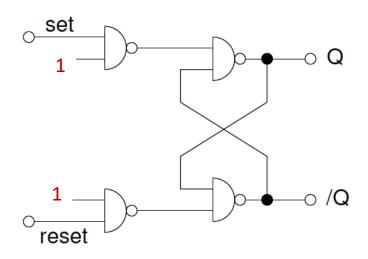

### Simple SR Latch

stable situation

Likewise, setting the reset to 1 and the set to 0, will lead to the inverse stable Situation

If the second inputs are 0, Q does not change latch is "opaque"

→ Gated or clocked SR latch

Flip flops (latches) are digital circuits with two stable states  $\rightarrow$  store information

Simple SR Latch

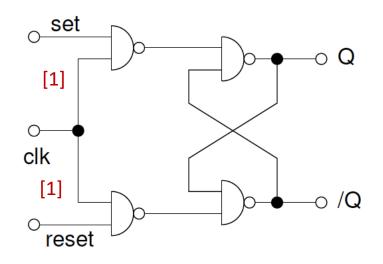

### Clocked SR Latch

clk provides "1" in a clocked way

Flip flops (latches) are digital circuits with two stable states → store information

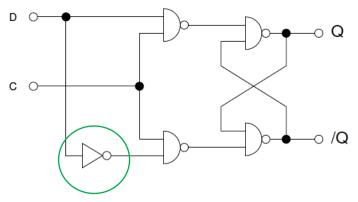

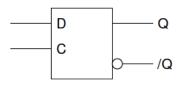

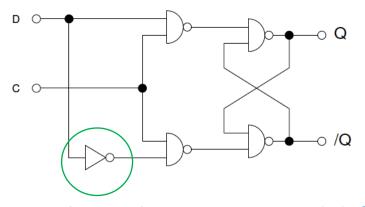

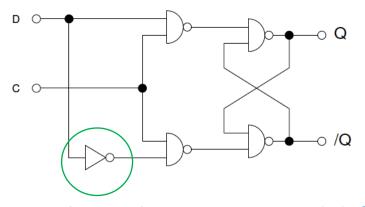

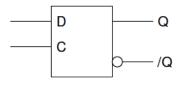

D- Latch: only "set" input needed, due to inverter

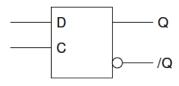

### symbol:

#### Truth table:

| С | D | Q                 | Q                 | Comment   |

|---|---|-------------------|-------------------|-----------|

| 0 | Х | Q <sub>prev</sub> | Q <sub>prev</sub> | No change |

| 1 | 0 | 0                 | 1                 | Reset     |

| 1 | 1 | 1                 | 0                 | Set       |

Flip flops (latches) are digital circuits with two stable states  $\rightarrow$  store information

D- Latch: only "set" input needed, due to inverter

symbol:

Flip flops (latches) are digital circuits with two stable states  $\rightarrow$  store information

D- Latch: only "set" input needed, due to inverter

symbol:

Flip flops (latches) are digital circuits with two stable states → store information

D- Latch: only "set" input needed, due to inverter

symbol:

Flip flops (latches) are digital circuits with two stable states  $\rightarrow$  store information

D- Latch: only "set" input needed, due to inverter

symbol:

(4) Circuit analysis, topologies

## Circuit analysis

Basic circuit analysis can be performed based on the two Kirchhoff laws:

Junction rule or Kirchhoff's Current Law (KCL):

The currents flowing out of any closed Region of a circuit sum to 0

$$\sum_{k=1}^{n} I_k = 0$$

$$I_3$$

$$I_4$$

$$I_5$$

$$I_6$$

Loop rule or Kirchhoff's Voltage Law (KVL):

The sum of voltage changes around a closed loop is 0

$$\sum_{k=1}^{n} U_k = 0$$

How can we apply these laws to calculate the circuits in an efficient way?

## Circuit analysis

Basic circuit analysis can be performed based on the two Kirchhoff laws:

## Junction rule or Kirchhoff's Current Law (KCL):

The currents flowing out of any closed Region of a circuit sum to 0

$$\sum_{k=1}^{n} I_k = 0$$

$$I_3$$

$$I_4$$

$$I_1$$

Loop rule or Kirchhoff's Voltage Law (KVL):

The sum of voltage changes around a closed loop is 0

$$\sum_{k=1}^{n} U_k = 0$$

How can we apply these laws to calculate the circuits in an efficient way?

- → Nodal analysis: identify nodes and applies KCL for each node

- → Mesh current analysis: identify essential meshes, assign mesh current and apply KVL

- → Thevenin equivalent: replace part of the network by source + resistance in series

- → Norton equivalent: replace part of the network by source and resistance in parallel

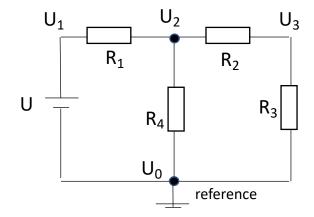

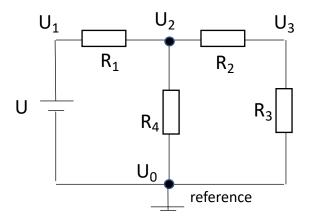

### Nodal Analysis

Node: section of the circuit which connects components. Aim: determine the voltage at each node relative to a reference node, then use them to derive the other relevant quantities

#### Steps:

- Identify all nodes and assign voltage variables (treat floating or dependent sources as super nodes with internal equation)

- Choose reference node

- Write a KCL equation at each node

- Solve the system of equations (e.g. via matrix inversion)

### Nodal Analysis

Node: section of the circuit which connects components. Aim: determine the voltage at each node relative to a reference node, then use them to derive the other relevant quantities

#### Steps:

- Identify all nodes and assign voltage variables (treat floating or dependent sources as super nodes with internal equation)

- Choose reference node

- Write a KCL equation at each node

- Solve the system of equations (e.g. via matrix inversion)

### Nodal Analysis

Node: section of the circuit which connects components. Aim: determine the voltage at each node relative to a reference node, then use them to derive the other relevant quantities

#### Steps:

- Identify all nodes and assign voltage variables (treat floating or dependent sources as super nodes with internal equation)

- Choose reference node

- Write a KCL equation at each node

- Solve the system of equations (e.g. via matrix inversion)

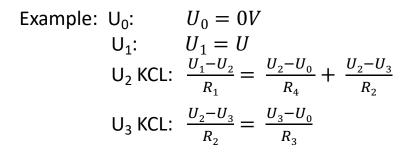

Example:

$$U_0$$

:  $U_0 = 0V$   $U_1$ :  $U_1 = U$   $U_2$  KCL:  $\frac{U_1 - U_2}{R_1} = \frac{U_2 - U_0}{R_4} + \frac{U_2 - U_3}{R_2}$   $U_3$  KCL:  $\frac{U_2 - U_3}{R_2} = \frac{U_3 - U_0}{R_2}$

- conveniently using conductance  $G = \frac{1}{R}$  -

- invert matrix or solve by substitution -

$$\rightarrow U_3 = \frac{G_1 G_2 U}{G_2 (G_1 + G_4) + G_3 (G_1 + G_2 + G_4)} \rightarrow U_2$$

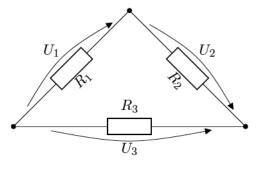

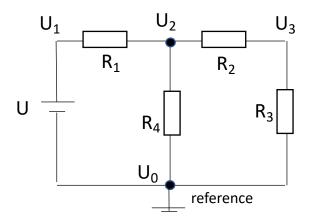

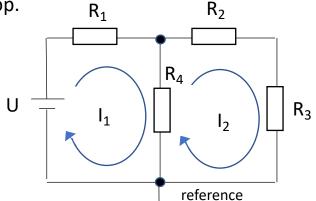

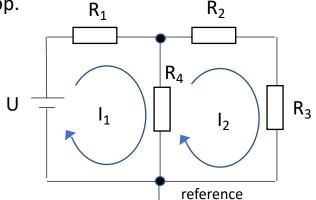

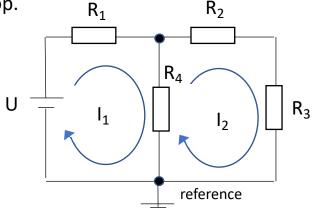

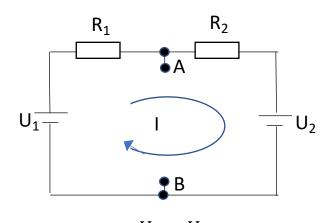

### Mesh current Analysis

Essential mesh: loop in the circuit that does not contain any other loop.

Aim: determine the current through each mesh then use them to derive the other relevant quantities

#### Steps:

- Identify all essential meshes and assign mesh current (special treatment for dependent sources and current sources which are part of two meshes)

- Apply the KVL for each mesh

- Solve the system of equations (e.g. via matrix inversion)

### Mesh current Analysis

Essential mesh: loop in the circuit that does not contain any other loop.

Aim: determine the current through each mesh then use them to derive the other relevant quantities

Steps:

- Identify all essential meshes and assign mesh current (special treatment for dependent sources and current sources which are part of two meshes)

- Apply the KVL for each mesh

- Solve the system of equations (e.g. via matrix inversion)

Example: Mesh 1:  $R_1I_1 + R_4(I_1 - I_2) = U$

Mesh 2:  $R_4(I_2 - I_1) + R_2I_2 + R_3I_2 = 0$

### Mesh current Analysis

Essential mesh: loop in the circuit that does not contain any other loop.

Aim: determine the current through each mesh

then use them to derive the other relevant quantities

#### Steps:

- Identify all essential meshes and assign mesh current (special treatment for dependent sources and current sources which are part of two meshes)

- Apply the KVL for each mesh

- Solve the system of equations (e.g. via matrix inversion)

Example: Mesh 1:

$$R_1I_1 + R_4(I_1 - I_2) = U$$

Mesh 2:

$$R_4(I_2 - I_1) + R_2I_2 + R_3I_2 = 0$$

$$\rightarrow \begin{bmatrix} R_1 + R_4 & -R_4 \\ -R_4 & R_2 + R_3 + R_4 \end{bmatrix} \begin{pmatrix} I_1 \\ I_2 \end{pmatrix} = \begin{pmatrix} U \\ 0 \end{pmatrix}$$

- invert matrix or solve by substitution -

$$\rightarrow I_1 = \frac{(R_2 + R_3 + R_4) U}{(R_1 + R_4)(R_2 + R_3 + R_4) - R_4^2} \rightarrow I_2$$

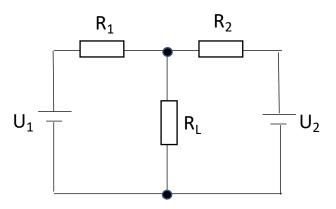

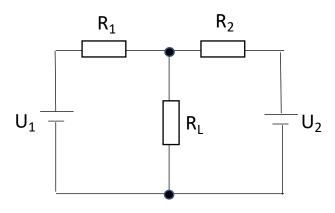

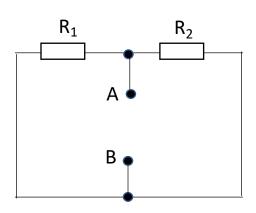

## Thevenin equivalent circuit

Thevenin's theorem: Any linear circuit containing several voltages and resistances can be replaced by just one single voltage in series with a single resistance connected across the load"

#### Example circuit:

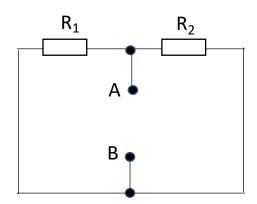

## Thevenin equivalent circuit

Thevenin's theorem: Any linear circuit containing several voltages and resistances can be replaced by just one single voltage in series with a single resistance connected across the load"

Example circuit:

Step1: remove load and shorten sources. Then calculate total Thevenin resistance R<sub>T</sub> wrt A/B

$$R_T = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2}$$

## Thevenin equivalent circuit

Thevenin's theorem: Any linear circuit containing several voltages and resistances can be replaced by just one single voltage in series with a single resistance connected across the load"

Example circuit:

$R_2$  $R_1$

Step1: remove load and shorten sources. Then calculate total Thevenin resistance R<sub>T</sub> wrt A/B

$$R_T = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2}$$

Step2: Reconnect sources. Calculate Thevenin voltage U<sub>T</sub>

$$I = \frac{U_1 - U_2}{R_1 + R_2}$$

$$U_T = UA_B = U_1 - IR_1 = U_2 + IR_2$$

$$= \frac{R_1 U_2 + U_1 R_2}{R_1 + R_2}$$

## Example: nodal analysis

### Revisiting Voltage divider biasing circuit

Reminder: The voltage U<sub>B</sub> across R<sub>2</sub> forward-biases the BE junction

Here: can use **nodal analysis**: Apply Kirchhoff's current law (KCL) at node 2

Reminder the  $I_B - U_B$  relation does not follow Ohms law but a diode-like input characteristics (which for this exercise, we pretend not to know)

U1:

$$U_1 = U_0$$

(1)

U2 KCL:  $I_1 = I_2 + I_R$  (2)

# Example: nodal analysis

### Revisiting Voltage divider biasing circuit

Reminder: The voltage U<sub>B</sub> across R<sub>2</sub> forward-biases the BE junction

Here: can use **nodal analysis**:

Apply Kirchhoff's current law (KCL) at node 2

Reminder the  $I_B - U_B$  relation does not follow Ohms law but a diode-like input characteristics (which for this exercise, we pretend not to know)

$$U_1$$

:  $U_1 = U_0$  (1)

$U_2$  KCL:  $I_1 = I_2 + I_B$  (2)

(1) & (2)

$$\Rightarrow \frac{U_0 - U_B}{R_1} = \frac{U_B}{R_2} + I_B \Rightarrow U_0 - U_B = U_B \frac{R_1}{R_2} + I_B R_1 \Rightarrow U_B \frac{R_1 + R_2}{R_2} = U_0 - I_B R_1$$

$\Rightarrow U_B = U_0 \frac{R_2}{R_1 + R_2} - I_B \frac{R_1 R_2}{R_1 + R_2}$

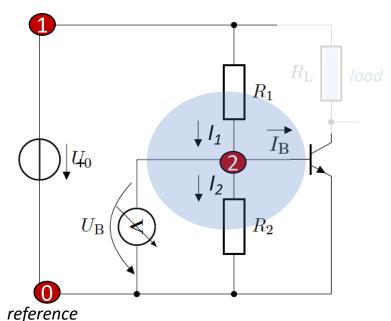

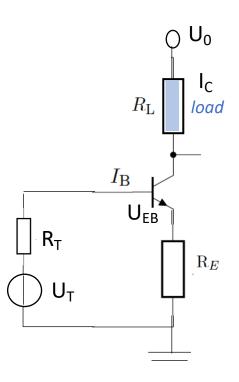

Voltage divider biasing with emitter resistance

Reminder: We can stabilize the working point by adding an emitter resistance

In order to simplify the calculations, we want to replace the voltage divider by the Thevenin equivalent

- Thevenin voltage:  $U_T = U_0 \frac{R_2}{R_1 + R_2}$

- The venin resistance:  $R_T = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2}$

Voltage divider biasing with emitter resistance

Reminder: We can stabilize the working point by adding an emitter resistance

In order to simplify the calculations, we want to replace the voltage divider by the Thevenin equivalent

- Thevenin voltage:

$$U_T = U_0 \frac{R_2}{R_1 + R_2}$$

- The venin resistance:

$$R_T = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2}$$

Voltage divider biasing with emitter resistance

Reminder: We can stabilize the working point by adding an emitter resistance

In order to simplify the calculations, we want to replace the voltage divider by the Thevenin equivalent

- Thevenin voltage:

$$U_T = U_0 \frac{R_2}{R_1 + R_2}$$

- The venin resistance:

$$R_T = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2}$$

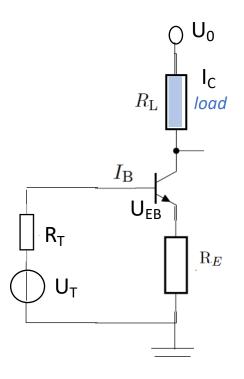

Now we can analyze the mesh (KVL):

$$U_T = I_B R_T + U_{BE} + R_E (I_B + Ic)$$

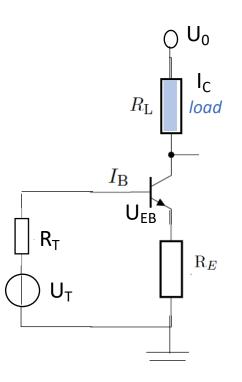

Voltage divider biasing with emitter resistance

Reminder: We can stabilize the working point by adding an emitter resistance

In order to simplify the calculations, we want to replace the voltage divider by the Thevenin equivalent

- Thevenin voltage:

$$U_T = U_0 \frac{R_2}{R_1 + R_2}$$

- The venin resistance:

$$R_T = R_1 || R_2 = \frac{R_1 R_2}{R_1 + R_2}$$

Now we can analyze the mesh (KVL):

$$U_T = I_B R_T + U_{BE} + R_E (I_B + Ic)$$

with  $I_C = \beta I_B$  (transfer characteristics):

$$U_T = I_B R_T + U_{BE} + RE I_B (1 + \beta)$$

$$\Rightarrow I_B = \frac{U_T - U_{BE}}{R_T + R_E (1 + \beta)} \Rightarrow I_C = \beta I_B \Rightarrow \dots$$

## Circuit topologies

The formal layout of the equations following the application of Kirchhoff's rules applied to a circuit does not depend on the type of device connected in the branches. It only depends on the topology of the circuit.

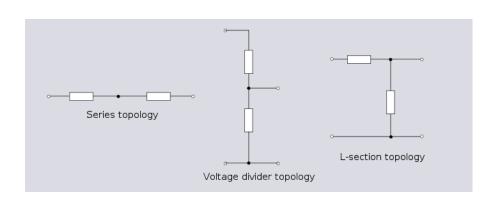

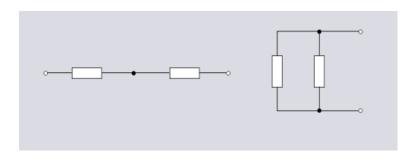

**Circuit Topology** describes how components in a network are connected. Circuits with different physical layout can have the same topology.

Example: three circuits with the same topology:

Example: There are only two topologies for a network with 2 branches: series and parallel.

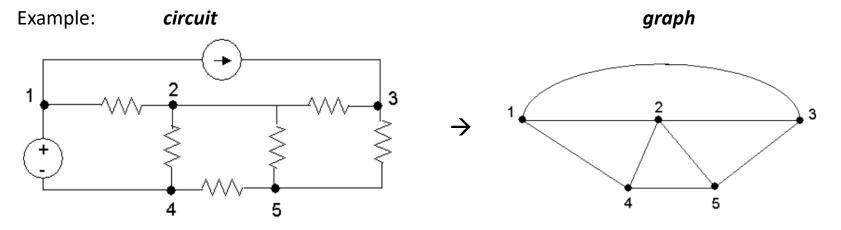

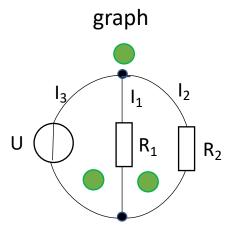

# Graph theory

Mathematical *Graph theory* is used to analyze the topology:

Graphs represents the aspects of a network connected to its topology. The devices are left out.

→ a line represents a device. A nod represents all points at the same potential.

The graph representation makes it easier to analyze complex circuits.

Graphs are *equivalent* if they can be transformed into each other by translation, rotation, reflection, stretching or crossing/knotting the branches,

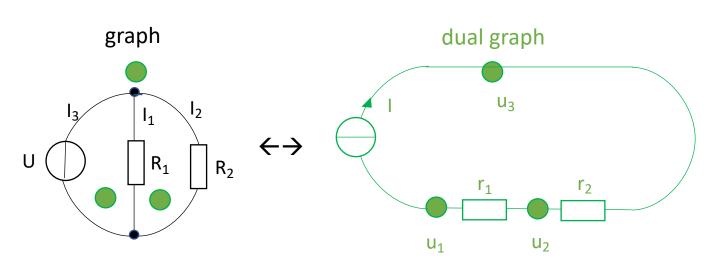

### Each graph has a **dual graph** with the following elements exchanged:

-  $R \leftarrow \rightarrow 1/R$

$U \leftarrow \rightarrow I$

- U source ← → I source

$-L \longleftrightarrow C$

-  $mesh \leftarrow \rightarrow node$

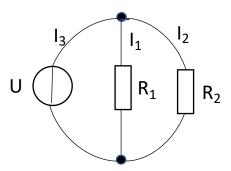

graph

$$I_3 = -I_1 - I_2 = U(\frac{1}{R_1} + \frac{1}{R_2})$$

Each graph has a **dual graph** with the following elements exchanged:

-  $R \leftarrow \rightarrow 1/R$

- U source ← → I source

-  $L \leftarrow \rightarrow C$

- mesh ← → node

—

- U ← → I

$$I_3 = -I_1 - I_2 = U(\frac{1}{R_1} + \frac{1}{R_2})$$

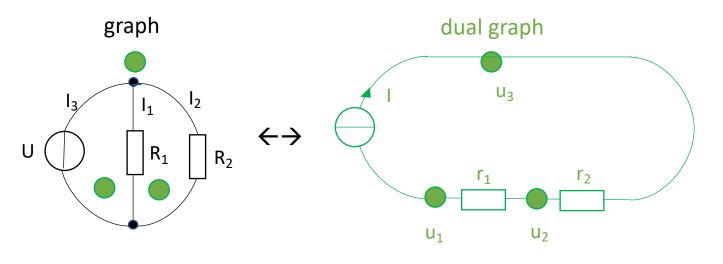

Each graph has a **dual graph** with the following elements exchanged:

-  $R \leftarrow \rightarrow 1/R$

$U \leftarrow \rightarrow I$

- U source ← → I source

-  $L \longleftrightarrow C$

mesh ← → node

converted parallel circuit into serial circuit

$$I_3 = -I_1 - I_2 = U(\frac{1}{R_1} + \frac{1}{R_2})$$

Each graph has a **dual graph** with the following elements exchanged:

$R \leftarrow \rightarrow 1/R$

U source  $\leftarrow \rightarrow$  I source

$L \leftarrow \rightarrow C$

mesh  $\leftarrow \rightarrow$  node

$U \leftarrow \rightarrow I$

converted parallel circuit into serial circuit

> both solutions are equivalent as  $U \leftarrow \rightarrow I$

$$I_3 = -I_1 - I_2 = U(\frac{1}{R_1} + \frac{1}{R_2})$$

$$I_3 = -I_1 - I_2 = U(\frac{1}{R_1} + \frac{1}{R_2})$$

$u_3 - u_1 = I(r_1 + r_2) = I(\frac{1}{R_1} + \frac{1}{R_2})$

### Introduction into Electronics

- (1) Reminder: Electrical circuits

- (2) Analog electronics

- (3) Digital electronics

- (4) Circuit analysis, circuit topologies